Abstract

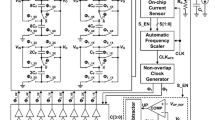

Dynamic voltage and frequency scaling (DVFS) is an efficient method to reduce the power consumption in system on-chip. To support DVFS, multiple supply voltages are generated based on different work load frequencies and currents using on-chip DC–DC voltage converter. In this paper a frequency tunable multiple output voltage switched capacitor based dc–dc converter is presented. An analog to digital converter and phase controller is used in the feedback to change the switching frequency and duty cycle of the converter. An input voltage of 1.8 V is converted to 0.6 and 0.8 V for low and high signal frequency respectively. The proposed 2-phase switched capacitor architecture with gain setting of 1:2 is designed with the 90 nm technology. An output ripple of 45 mV is observed and the maximum transient response time of the converter is 17.3 ns (= 58 MHz).

Similar content being viewed by others

References

Ma, D., & Luo, F. (2008). Robust multiple-phase switched-capacitor DC–DC power converter with digital interleaving regulation scheme. IEEE Transactions on Very Large Scale Integration (VLSI) Systems, 16(6), 611–619.

Salem L., & Ismail Y. (2010). Fully integrated fast response switched-capacitor DC-DC converter using reconfigurable interleaving. Paper presented at the International Conference on Energy Aware Computing, ICEAC 2010.

Chen Y., & Liu K. (2010). The switched-capacitor step-down DC–DC converter with improved voltage stability and load range. Paper presented at the Proceedings of the 5th IEEE Conference on Industrial Electronics and Applications, ICIEA 2010 (pp. 1389–1393).

Chowdhury, I., &Ma, D. (2008). An integrated reconfigurable switched-capacitor dc–dc converter with a dual-loop adaptive gain-pulse control. Paper presented at the Proceedings of the IEEE International Symposium on Circuits and Systems (pp. 2610–2613).

Bhattacharyya K., & Mandal, P. (2008). A low voltage, low ripple, on chip, dual switch-capacitor based hybrid DC–DC converter. Paper presented at the Proceedings of the IEEE International Frequency Control Symposium and Exposition (pp. 661–666).

Zhang, X., Pu, Y., Ishida, K., Ryu, Y., Okuma, Y., Chen, P., & Takamiya, M. (2010). A 1-V input, 0.2 to 0.47-V output switched-capacitor DC–DC converter with pulse density and width modulation (PDWM) for 57% ripple reduction. Paper presented at the IEEE Asian Solid-State Circuits Conference, A-SSCC (pp. 61–64).

Ma, D. (2006). Robust multiple-phase switched-capacitor DC–DC converter with digital interleaving regulation scheme. Paper presented at the Proceedings of the International Symposium on Low Power Electronics and Design (pp. 400–405).

Ramadass, Y. K., Fayed, A., & Chandrakasan, A. P. (2010). A fully-integrated switched-capacitor step-down DC–DC converter with digital capacitance modulation in 45 nm CMOS. IEEE Journal of Solid State Circuits, 45(12), 2557–2565.

Jung, I., Kim, Y., & Choi, M. (2011). The novel switched-capacitor DC–DC converter for fast response time and reduced ripple. Paper presented at the Midwest Symposium on Circuits and Systems.

Jeon, H., & Kim, Y. (2012). A fully integrated switched-capacitor DC–DC converter with dual output for low power application. Paper presented at the Proceedings of the ACM Great Lakes Symposium on VLSI, GLSVLSI (pp. 83–86).

Wibben, Josh, & Harjani, Ramesh. (2008). A high efficiency DC–DC converter using 2 nH integrated inductors. IEEE Journal of Solid State Circuits, 43(4), 844–854.

Djara, V., Deshpande, V., Sousa, M., Caimi, D., Czornomaz, L., & Fompeyrine, J. (2016). CMOS-compatible replacement metal gate InGaAs-OI FinFETWith ION = 156 µA/µm at VDD = 0.5 V and IOFF = 100 nA/µm. IEEE Electron Device Letters, 37(2), 169–172.

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Naidu, K.J., Kittur, H.M. Frequency tunable low ripple and fast response on-chip DC–DC converter for DVFS. Analog Integr Circ Sig Process 90, 639–644 (2017). https://doi.org/10.1007/s10470-016-0905-z

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10470-016-0905-z