Abstract

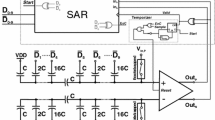

A 10-bit 50 MS/s current-mode based SAR ADC is presented in this paper. The SAR ADC uses a Gm stage which converts the input voltage to a current which is then processed in a current based binary search algorithm SAR loop. Due to the absence of a switched capacitor feedback DAC, the value of the sampling capacitance can be chosen solely based on the kT/C noise required to achieve a certain performance. Then by designing the input Gm stage for a wide differential input voltage range, the resulting sampling capacitance value can be made significantly smaller compared to a conventional switched capacitor SAR ADC. Moreover, the presented design requires neither an external reference voltage to bias the Gm stage output nor a low-impedance DAC-reference voltage. To validate the proposed approach, a prototype 10-bit ADC is fabricated in a 90 nm TSMC CMOS process. Measured results of the ADC show an SFDR of 58.4 dB at 50 MS/s, while consuming 6 mW from a 1.2 /1.8 V supply.

Similar content being viewed by others

References

Sung, B-R-S., Jo, D-S., Jang, I-H. et al. (2015). A 21 fJ/conversion-step 9 ENOB 1.6 GS/s 2x time-interleaved FATI SAR ADC with background offset and timing-skew calibration in a 45 nm CMOS. In IEEE International Solid-State Circuits Conference Digest of Technical Papers (ISSCC) (pp. 464–465), Feburary, 2015.

Hong, H-K., Kang, H-W., & Jo, D-S. et al. (2015). 26.7 A 2.6 b/cycle-architecture-based 10 b 1.7 GS/s 15.4 mW 4x-time-interleaved SAR ADC with a multistep hardware-retirement technique. In IEEE International Solid-State Circuits Conference Digest of Technical Papers (ISSCC) (pp. 1–3), Feburary 22–26, 2015.

Kramer, M., Janssen, E., Doris, K., & Murmann, B. (2015). 15.7 14 b 35 MS/S SAR ADC achieving 75 dB SNDR and 99 dB SFDR with loop-embedded input buffer in 40nm CMOS. In IEEE International Solid-State Circuits Conference Digest of Technical Papers (ISSCC) (pp. 1–3), Feburary 22–26, 2015.

Doris, K., Janssen, E., Nani, C., Zanikopoulos, A., et al. (2011). A 480 mW 2.6 GS/s 10b time-interleaved ADC with 48.5 dB SNDR up to nyquist in 65 nm CMOS. In IEEE J. of Solid-State Circuits (JSSC), vol. 46, no. 12, pp. 2821, 2833, Dec. 2011.

Janssen, E., Doris, K., Zanikopoulos, A. et al. (2013). An 11b 3.6GS/s time-interleaved SAR ADC in 65nm CMOS. In IEEE International in Solid-State Circuits Conference Digest of Technical Papers (ISSCC) (pp. 464–465), Feburary 17–21, 2013.

Elkafrawy, A., Anders, J., Brückner, T., & Ortmanns, M. (2013). Design of a current steering DAC for a high speed current mode SAR ADC. In 20th IEEE International Conference on Electronics, Circuits and Systems (ICECS) (pp. 441–444), December, 2013.

Elkafrawy, A., Anders, J., & Ortmanns, M. (2015). A 10-bit 150 MS/s current mode SAR ADC in 90 nm CMOS. In 11th IEEE Conference on PhD Research in Microelectronics and Electronics (PRIME) June, 2015.

Elkafrawy, A., Anders, J., & Ortmanns, M. (2015). A 10-bit reference free current mode SAR ADC with 58.4 dB SFDR at 50 MS/s in 90 nm CMOS. In Nordic Circuits and Systems Conference (NORCAS): NORCHIP & International Symposium on System-on-Chip (SoC) (pp. 1–4), October 26–28, 2015.

Haaheim, B. & Constandinou, T.G. (2012). A sub-1 μW, 16 kHz current-mode SAR-ADC for single-neuron spike recording. In IEEE International Symposium on Circuits and Systems (ISCAS) (pp. 2957–2960), May, 2012.

Tang, X. & Pun, K.P. “A novel switched-current successive approximation ADC” J. of Circuits, Systems and Computers, Vol. 20, Issue 1, pp. 15-27, Feb. 2011.

Shenoy, M.V., Varghese, K.S., & Upadhyaya, M.S. (2014). A 8-bit SAR ADC using current mode approach for bio-medical applications. In National Conference on Communication, Signal Processing and Networking (NCCSN) (pp. 1–5), October 10–12, 2014.

Al-Ahdab, S., Lotfi, R., & Serdijn, W.A. (2010). A 1-V 225-nW 1KS/s current successive approximation ADC for pacemakers. In IEEE Conference on Ph.D. Research in Microelectronics and Electronics (PRIME) (pp. 1–4), July 18–21, 2010.

Yang, Z. & Van der Spiegel, J. (2008). A 10-bit 8.3MS/s switched current successive approximation adc for column-parallel imagers. In IEEE International Symposium on Circuits and Systems (ISCAS) (pp. 224–227), May, 2008.

Długosz, R. & Iniewski, K. (2007). Flexible architecture of ultra-low-power current-mode interleaved successive approximation analog-to-digital converter for wireless sensor networks VLSI Design. Article ID 45269, 13 pages, 2007.

Liu, C.-C., Chang, S.-J., Huang, G.-Y., et al. “A 10-bit 50-MS/s SAR ADC with a monotonic capacitor switching procedure,” IEEE J. of Solid-State Circuits (JSSC), vol. 45, no. 4, pp. 731, 740, April 2010.

Elkafrawy, A., AlMarashli, A., Anders, J., & Ortmanns, M. (2014). Design of a high linearity Gm stage for a high speed current mode SAR ADC. In 21st IEEE International Conference on Electronics, Circuits and Systems (ICECS) (pp. 136–139), December 7–10, 2014.

Sanchez-Sinencio, E., & Silva-Martinez, J. (2000). CMOS transconductance amplifiers, architectures and active filters: a tutorial. IEE Proceedings-Circuits, Devices and Systems, 147(1), 3–12.

Elkafrawy, A., Anders, J., & Ortmanns, M. (2014). A high resolution transimpedance amplifier for use in a 10-bit 200 MS/s current mode SAR ADC. In 57th IEEE International Midwest Symposium on Circuits and Systems (MWSCAS) (pp. 1057–1060), August 3–6, 2014.

Kim, C., Kim, Y., & Park, S. (1992), "New cmos linear transconductor" Electronics Letters, 28(21), 1962–1964.

Wikner, J.J., & Tan, N. (1999) “Modeling of CMOS digital-to-analog converters for telecommunication,” IEEE Transactions on Circuits and Systems II: Analog and Digital Signal Processing, vol. 46, no. 5, pp. 489–499.

Van den Bosch, A., Borremans, M.A.F., Steyaert, M.S.J., & Sansen, W. (2001) “A 10-bit 1-Gsample/s nyquist current-steering CMOS D/A converter,” IEEE J. of Solid-State Circuits (JSSC), vol. 36, no. 3, pp. 315–324.

Pelgrom, M.J.M., Duinmaijer, Aad C.J., & Welbers, A.P.G. (1989) “Matching properties of MOS transistors,” IEEE J. of Solid-State Circuits (JSSC), vol. 24, no. 5, pp. 1433–1439.

Sackinger, E. (2010) “The transimpedance limit,”IEEE Transactions on Circuits and Systems I: Regular Papers, vol. 57, no. 8, pp. 1848–1856.

Liao, C.-F., & Liu, S.-I. (2008) “40 Gb/s transimpedance-AGC amplifier and CDR circuit for broadband data receivers in 90 nm CMOS,” IEEE J. of Solid-State Circuits (JSSC), vol. 43, no. 3, pp. 642–655.

Park, S.M., & Yoo, H.-J. (2004) “1.25-Gb/s regulated cascode CMOS transimpedance amplifier for gigabit ethernet applications,” IEEE J. of Solid-State Circuits (JSSC), vol. 39, no. 1, pp. 112–121.

Oliveira, L.B., Leitao, C.M., Silva, M.M. (2012) “Noise performance of a regulated cascode transimpedance amplifier for radiation detectors,” IEEE Transactions on Circuits and Systems I: Regular Papers, vol. 59, no. 9, pp. 1841–1848.

Zhu, Y.,Chan, C.-H., Chio, U.-F., et al. (2010) “A 10-bit 100-MS/s reference-free SAR ADC in 90 nm CMOS,” IEEE J. of Solid-State Circuits (JSSC), vol. 45, no. 6, pp. 1111–1121.

Liu, C-C., Chang, S-J., Huang, G-Y., et al. (2010). A 10 b 100 MS/s 1.13 mW SAR ADC with binary-scaled error compensation, IEEE International Solid-State Circuits Conference Digest of Technical Papers (ISSCC) (pp. 386–387), Feburary 7–11, 2010.

Malki, B., Yamamoto, T., Verbruggen, B., et al. (2014). “A 70 dB DR 10 b 0-to-80 MS/s current-integrating SAR ADC with adaptive dynamic range”. IEEE J. of Solid-State Circuits (JSSC), 49(5), 1173–1183.

Miki, T., Morie, T., Matsukawa, K., et al. (June 2015). “A 4.2 mW 50 MS/s 13 bit CMOS SAR ADC with SNR and SFDR enhancement techniques.” IEEE J. of Solid-State Circuits (JSSC), 50(6), 1372–1381.

Kapusta, R., Junhua, S., & Decker, S. et al. (2013). A 14-bit, 80 MS/s SAR ADC with 73.6 dB SNDR in 65 nm CMOS,” IEEE International Solid-State Circuits Conference Digest of Technical Papers (ISSCC) (pp. 472–473), Feburary, 2013.

Inerfield, M., & Kamath, A. et al. (2014). An 11.5-ENOB 100-MS/s 8 mW dual-reference SAR ADC in 28 nm CMOS,” Symposium on VLSI Circuits Digest of Technical Papers (pp. 192–193), June, 2014.

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Elkafrawy, A., Anders, J. & Ortmanns, M. Design and validation of a 10-bit current mode SAR ADC with 58.4 dB SFDR at 50 MS/s in 90 nm CMOS. Analog Integr Circ Sig Process 89, 283–295 (2016). https://doi.org/10.1007/s10470-016-0788-z

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10470-016-0788-z