Abstract

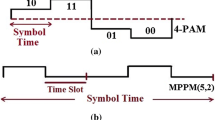

This paper proposes a new multi level of amplitude and pulse width (PW) modulation structure for a 7Gb/s serial link transceiver. This scheme can be implemented in 0.18 m CMOS technology. Applying this technique, 7 bit data is embedded in a symbol time. Therefore the symbol rate is reduced, while the minimum PW is increased. In the proposed structure, the PW is larger than Tb (a conventional NRZ data PW). Therefore, the ISI will be improved. The multiphase output of a five stage ring oscillator VCO in the PLL is used to modulate and demodulate the signal. In PAM modulator block, a current-mode technique is used to increase the rate of data transmission. Serialization of parallel data is established by a current-mode multiplexer. At the receiver part, a novel high-speed comparator is proposed to demodulate the data signal. In addition, to reinforce the incoming signal, a preamplifier with high gain and high bandwidth is proposed. PWAM modulator, which consists of a PWM modulator and a PAM modulator blocks, consumes 71 mW. The receiver block power consumption is about 14 mW.

Similar content being viewed by others

References

Farjad-Rad, R., et al. (2000). A 0.3 um CMOS 8-Gb/s 4-PAM serial link transceiver. IEEE Journal of Solid-state Circuits, 35, 757–763.

Farzan, K., & Johns, D. A. (2004). A CMOS 10-Gb/s power-efficient 4- PAM transmitter. IEEE Journal of Solid-state Circuits, 39, 529–532.

Li, M., & Yuan, F. (2005). A new fully differential 4-PAM current- mode transmitter for 10 Gb/s serial links in 0.13 um, midwest symposium on circuits and systems, Covington, MWCAS, 1665–1668.

Chen, W. H., Dehng, G. K., Chen, J. W., & Liu, S. I. (2001). A CMOS 400-Mb/s serial sink for AS-memory systems using a PWM scheme. IEEE Journal of Solid-state Circuits, 36(10), 1498–1505.

Yang, C. Y., & Lee, Y. (2008). A PWM and PAM signaling hybrid technology for serial-link transceivers. IEEE Transactions on Instrumentation and Measurement, 57, 1058–1070.

Ghaderi, N., Hadidi, Kh, & Khoei, Kh. (2012). A CMOS 3.2 GB/s serial link transceiver using a new PWAM scheme. Journal of Analog Integrated Circuit and Signal Processing, 71, 421–432.

Bae, W., & Yoo, B-j. (2012). Design of CMOS 5Gb/s 4-PAM transceiver Front-end for low-power memory interface, international SOC design conference, Gyeongju, ISOCC, (pp. 49–52).

Song, B., & Kim, K. (2014). A 13.5-mW 10-Gb/s 4-PAM serial link transmitter scheme. IEEE Transaction on Circuits and Systems II, 61, 646–650.

Yuan, F. (2004). A fully differential 8-to-l current-mode multiplexer for 10 Gbps serial links in 0.18 m CMOS. lEE Electronics Letters, 40(13), 789–790.

Jiang, J., & Yuan, F. (2005). A new CMOS current-mode multiplexer for lOGbps serial links. Analog Integrated Circuits and Signal Processing, 44(1), 61–67.

Yuan, F. (2008). CMOS active inductors and transformers principle, implementation and applications. New York Springer Science+Business Media.

Dorostghol1, Z., Ghaderi, N., & Ebnali-Heidari, M. (2015). A novel high gain-bandwidth product and low power band-pass preamplifier using active inductor, 9th international conference on electrical and electronics engineering, ELECO, Bursa, TURKEY.

Erfani Jazi, H. R., & Ghaderi, N. (2015). A divider-less high speed and wide locking range phase locked loop. International Journal of Electronics and Communications, 69, 722–729.

Bao-Ni, H., Yin-Tang, Y., & Zhang-Ming, Z. (2008). A novel l.25 GSPS ultra high-speed comparator in 0.18-\(\upmu {\rm m}\) CMOS, IEEE 9th international conference on solid-state and integrated-circuit technology, (pp. 1957–1960).

Shar, A. (2007). Design of a high-speed CMOS comparator, master thesis in electronics system, Department of Electrical Engineering, Linkoping University.

Yewale, Sh, & Gamad, R. (2012). Design of low power and high speed CMOS comparator for A/D converter application. Wireless Engineering and Technology, 2, 90–95.

Zhang, Sh., Li, Zh., & Ling, B. (2012) Design of high-speed and low-power comparator in flash ADC, 2012 international workshop on information and electronics engineering (IWIEE), 29, (pp. 687–692).

Kim, M. (2014). Electrical characterization on signal transmission of SATA cable assembly. International Journal of Control and Automation, 7, 173–180.

Song, B., Kim, K., Lee, J., & Burm, J. (2013). A 0.18-\(\upmu {\rm m}\) CMOS 10-Gb/s dual-mode 10-PAM serial link transceiver. IEEE Transaction on Circuits and Systems I, 60, 457–468.

Niitsu, K., Osawa, Y., Harigai, N., Hirabayashi, D., Kobayashi, O., Yamaguchi, T. J., et al. (2015). A CMOS PWM transceiver using self-referenced edge detection. IEEE Transactions on very Large Scale Integration (VLSI) Systems, 23, 1145–1149.

Kim, Y. B., & Kim, Y. B. (2010). Design and noise analysis of 8Gb/s capacitive low power and high speed 4-PWAM transceiver, 53rd IEEE international midwest symposium on circuits and systems.

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Ghaderi, N., Ghol, Z.D. & Fatemi, S.R. A CMOS 7Gb/s, 4-PAM and 4-PWM, serial link transceiver. Analog Integr Circ Sig Process 89, 809–823 (2016). https://doi.org/10.1007/s10470-016-0779-0

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10470-016-0779-0