Abstract

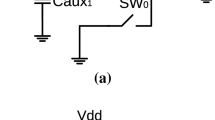

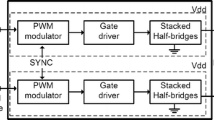

This paper reviews the state-of-the-art of high switching frequency, integrated DC–DC converters and presents the main trade-offs and challenges emerging from this review. Various converter structures (1-phase buck, 2-phase buck, 2-phase coupled buck and 3-level converter) are then discussed and analyzed through simulation from a losses point-of-view. Considering the review, the architecture analysis and the technology model, 4 converters are designed for a given set of specifications: 3.3–1.2 V, 280 mA output current at high switching frequency (100–200 MHz) in 40 nm bulk CMOS. A cascode power stage is used in order to enhance power conversion efficiency, and 1-phase and 2-phase structures are designed. Post-layout simulation results are presented, showing an efficiency above 90 % for a 2-phase converter.

Similar content being viewed by others

References

Abedinpour, S., Bakkaloglu, B., & Kiaei, S. (2007). A multistage interleaved synchronous buck converter with integrated output filter in 0.18 μm SiGe process. IEEE Transactions on Power Electronics, 22(6), 2164–2175. doi:10.1109/TPEL.2007.909288.

Alimadadi, M., Sheikhaei, S., Lemieux, G., Mirabbasi, S., Dunford, W., & Palmer, P. (2009). A fully integrated 660 MHz low-swing energy-recycling DC–DC converter. IEEE Transactions on Power Electronics, 24(6), 1475–1485. doi:10.1109/TPEL.2009.2013624.

Bathily, M., Allard, B., & Hasbani, F. (2012). A 200-MHz integrated buck converter with resonant gate drivers for an RF power amplifier. IEEE Transactions on Power Electronics, 27(2), 610–613. doi:10.1109/TPEL.2011.2119380.

Bergveld, H., Nowak, K., Karadi, R., Iochem, S., Ferreira, J., Ledain, S., Pieraerts, E., Pommier, M. (2009). A 65-nm-CMOS 100-MHz 87%-efficient DC–DC down converter based on dual-die system-in-package integration. In: Energy conversion congress and exposition, 2009. ECCE 2009. IEEE, pp. 3698–3705. DOI 10.1109/ECCE.2009.5316334.

Blanken, P., Karadi, R., Bergveld, H. (2008). A 50MHz bandwidth multi-mode PA supply modulator for GSM, EDGE and UMTS application. In: Radio frequency integrated circuits symposium, 2008. RFIC 2008. IEEE, pp. 401–404. DOI 10.1109/RFIC.2008.4561463.

Burton, E., Schrom, G., Paillet, F., Douglas, J., Lambert, W., Radhakrishnan, K., Hill, M. (2014). FIVR - Fully integrated voltage regulators on 4th generation Intel Core SoCs. In: Applied power electronics conference and exposition (APEC), 2014 29th annual IEEE, pp. 432–439. DOI 10.1109/APEC.2014.6803344.

Gong, X., Ni, J., Hong, Z., Liu, B. (2011). An 80% Peak efficiency, 0.84 mW sleep power consumption, fully-integrated DC–DC converter with Buck/LDO mode control. In: Custom integrated circuits conference (CICC), 2011 IEEE, pp. 1–4. DOI 10.1109/CICC.2011.6055338.

Hannon, J., Foley, R., Griffiths, J., O’Sullivan, D., McCarthy, K., Egan, M. (2009). A 20 MHz 200–500 mA monolithic buck converter for RF applications. In: Applied power electronics conference and exposition, 2009. APEC 2009. 24th Annual IEEE, pp. 503–508. DOI 10.1109/APEC.2009.4802705.

Hazucha, P., Schrom, G., Hahn, J., Bloechel, B., Hack, P., Dermer, G., et al. (2005). A 233-MHz 80%87% efficient four-phase DCDC converter utilizing air-core inductors on package. IEEE Journal of Solid-State Circuits, 40(4), 838–845. doi:10.1109/JSSC.2004.842837.

Huang, C., Mok, P.: A 100 MHz 82.4% Efficiency Package-Bondwire Based Four-Phase Fully-Integrated Buck Converter With Flying Capacitor for Area Reduction. In: Solid-State Circuits Conference Digest of Technical Papers (ISSCC), 2013 IEEE International, pp. 362–363 (2013). DOI 10.1109/ISSCC.2013.6487770.

Ishida, K., Takemura, K., Baba, K., Takamiya, M., Sakurai, T.: 3D Stacked Buck Converter with 15 μm Thick Spiral Inductor on Silicon Interposer for Fine-Grain Power-Supply Voltage Control in SiP’s. In: 3D Systems Integration Conference (3DIC), 2010 IEEE International, pp. 1–4 (2010). DOI 10.1109/3DIC.2010.5751437.

Kim, W., Brooks, D., & Wei, G. Y. (2012). A fully-integrated 3-Level DC–DC converter for nanosecond-scale DVFS. IEEE Journal of Solid-State Circuits, 47(1), 206–219. doi:10.1109/JSSC.2011.2169309.

Krishnamurthy, H., Vaidya, V., Kumar, P., Matthew, G., Weng, S., Thiruvengadam, B., Proefrock, W., Ravichandran, K., De, V.: A 500 MHz, 68% Efficient, Fully On-Die Digitally Controlled Buck Voltage Regulator on 22 nm Tri-Gate CMOS. In: VLSI Circuits Digest of Technical Papers, 2014 Symposium on, pp. 1–2 (2014). DOI 10.1109/VLSIC.2014.6858438.

Kudva, S., & Harjani, R. (2011). Fully-integrated on-chip DC–DC converter with a 450X output range. IEEE Journal of Solid-State Circuits, 46(8), 1940–1951. doi:10.1109/JSSC.2011.2157253.

Lallemand, F., Voiron, F.: Silicon Interposers with Integrated Passive Devices, an Excellent Alternative to Discrete Components. In: Microelectronics Packaging Conference (EMPC), 2013 European, pp. 1–6 (2013).

Li, P., Bhatia, D., Xue, L., & Bashirullah, R. (2011). A 90–240 MHz hysteretic controlled DC–DC buck converter with digital PLL synchronization. IEEE Journal of Solid-State Circuits, 46(9), 2108–2119. doi:10.1109/JSSC.2011.2139550.

Li, Q. (2012). A fully-integrated buck converter design and implementation for on-chip power supplies. Journal of Computers, 7(5), 1270–1277. doi:10.4304/jcp.7.5.1270-1277.

Lu, D., Yu, J., Hong, Z., Mao, J., Zhao, H. (2012). A 1500 mA, 10 MHz on-time controlled buck converter with ripple compensation and efficiency optimization. In: Applied power electronics conference and exposition (APEC), 2012 27th Annual IEEE, pp. 1232–1237. DOI 10.1109/APEC.2012.6165976.

Maity, A., Patra, A., Yamamura, N., Knight, J. (2011). Design of a 20 MHz DC-DC buck converter with 84% efficiency for portable applications. In: 24th International Conference on VLSI Design (VLSI Design), pp. 316–321. DOI 10.1109/VLSID.2011.37.

Mathuna, S., O’Donnell, T., Wang, N., & Rinne, K. (2005). Magnetics on silicon: An enabling technology for power supply on chip. IEEE Transactions on Power Electronics, 20(3), 585–592.

Onizuka, K., Kawaguchi, H., Takamiya, M., Sakurai, T.: Stacked-chip implementation of on-chip buck converter for power-aware distributed power supply systems. In: Solid-State Circuits Conference, 2006. ASSCC 2006. IEEE Asian, pp. 127–130 (2006). doi:10.1109/ASSCC.2006.357868

Ostman, K., Jarvenhaara, J., Broussev, S., Viitaniemi, I.: A 3.6-to-1.8-V Cascode Buck Converter With a Stacked LC Filter in 65-nm CMOS. Circuits and Systems II: IEEE Transactions on Express Briefs, PP(99), 1–5 (2014). doi:10.1109/TCSII.2014.2304875

Peng, H., Anderson, D., & Hella, M. (2013). A 100 MHz two-phase four-segment DC–DC converter with light load efficiency enhancement in 0.18 \({{\mu }}\)m CMOS. IEEE Trans. Circuits Syst. I, 60(8), 2213–2224. doi:10.1109/TCSI.2013.2239157.

Peng, H., Pala, V., Wright, P., Chow, T., & Hella, M. (2011). High efficiency, high switching speed, AlGaAs/GaAs P-HEMT DCDC converter for integrated power amplifier modules. Analog Integr. Circuits Signal Process., 66, 331–348. doi:10.1007/s10470-010-9543-z.

Schrom, G., Hazucha, P., Hahn, J., Gardner, D., Bloechel, B., Dermer, G., Narendra, S., Karnik, T., De, V.: A 480-MHz, Multi-Phase Interleaved Buck DC-DC Converter with Hysteretic Control. In: Power Electronics Specialists Conference, 2004. PESC 04. 2004 IEEE 35th Annual, vol. 6, pp. 4702–4707 Vol. 6 (2004). doi:10.1109/PESC.2004.1354830

Schrom, G., Hazucha, P., Paillet, F., Rennie, D.J., Moon, S.T., Gardner, D.S., Kamik, T., Sun, P., Nguyen, T.T., Hill, M.J., Radhakrishnan, K., Memioglu, T.: A 100MHz Eight-Phase Buck Converter Delivering 12 A in 25 mm\(^{2}\) Using Air-Core Inductors. In: Applied Power Electronics Conference, APEC 2007 - Twenty Second Annual IEEE, pp. 727–730 (2007). doi:10.1109/APEX.2007.357595

Song, M.K., Dehghanpour, M.F., Sankman, J., Ma, D.: A VHF-Level Fully Integrated Multi-Phase Switching Converter Using Bond-Wire Inductors and On-Chip Decoupling Capacitors and DLL Phase Synchronization. In: 2014 Twenty-Ninth Annual IEEEApplied Power Electronics Conference and Exposition (APEC) (2014)

Song, M.K., Sankman, J., Ma, D.: A 6A 40MHz Four-Phase ZDS Hysteretic DC-DC Converter with 118mV Droop and 230ns Response Time for a 5A/5ns Load Transient. In: Solid-State Circuits Conference Digest of Technical Papers (ISSCC), 2014 IEEE International, pp. 80–81 (2014). doi:10.1109/ISSCC.2014.6757346

Souvignet, T., Allard, B., Trochut, S., Hasbani, F.: A Simple Approach to a Linear Control of Switched Capacitor DC-DC Converters in System-on-Chip. In: Control and Modeling for Power Electronics (COMPEL), 2014 IEEE 15th Workshop on, pp. 1–7 (2014). doi:10.1109/COMPEL.2014.6877205

Sturcken, N., O’Sullivan, E., Wang, N., Herget, P., Webb, B., Romankiw, L., et al. (2013). A 2.5D integrated voltage regulator using coupled-magnetic-core inductors on silicon interposer. IEEE J. Solid-State Circuits, 48(1), 244–254. doi:10.1109/JSSC.2012.2221237.

Sturcken, N., Petracca, M., Warren, S., Carloni, L., Peterchev, A., Shepard, K.: An Integrated Four-Phase Buck Converter Delivering 1A/mm2 with 700ps Controller Delay and Network-on-Chip Load in 45-nm SOI. In: Custom Integrated Circuits Conference (CICC), 2011 IEEE, pp. 1–4 (2011). doi:10.1109/CICC.2011.6055336

Sun, J., Lu, J.Q., Giuliano, D., Chow, T., Gutmann, R.: 3D Power Delivery for Microprocessors and High-Performance ASICs. In: Applied Power Electronics Conference, APEC 2007 - Twenty Second Annual IEEE, pp. 127–133 (2007). doi:10.1109/APEX.2007.357505

Villar, G., Alarcon, E.: Monolithic Integration of a 3-Level DCM-Operated Low-Floating-Capacitor Buck Converter for DC-DC Step-Down Conversion in Standard CMOS. In: Power Electronics Specialists Conference, 2008. PESC 2008. IEEE, pp. 4229–4235 (2008)

Wens, M., Steyaert, M.: A Fully-Integrated 0.18 \({{\mu }}\)m CMOS DC-DC Step-Down Converter, Using a Bondwire Spiral Inductor. In: Custom Integrated Circuits Conference, 2008. CICC 2008. IEEE, pp. 17–20 (2008). doi:10.1109/CICC.2008.4672009

Wens, M., & Steyaert, M. (2011). A fully integrated CMOS 800-mW four-phase semiconstant ON/OFF-time step-down converter. IEEE Trans. Power Electron., 26(2), 326–333. doi:10.1109/TPEL.2010.2057445.

Wens, M., Steyaert, M.: Basic DC-DC Converter Theory. In: Design and Implementation of Fully-Integrated Inductive DC-DC Converters in Standard CMOS, Analog Circuits and Signal Processing, pp. 27–63. Springer, Netherlands (2011). doi:10.1007/978-94-007-1436-6_2

Wibben, J., & Harjani, R. (2008). A high-efficiency DC–DC converter using 2 nH integrated inductors. IEEE J. Solid-State Circuits, 43(4), 844–854. doi:10.1109/JSSC.2008.917321.

Acknowledgments

This work is supported by the European Commission through the Seventh Framework Programme (FP7), under the Project Grant PowerSWIPE No. 318529.

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Neveu, F., Allard, B. & Martin, C. A review of state-of-the-art and proposal for high frequency inductive step-down DC–DC converter in advanced CMOS. Analog Integr Circ Sig Process 87, 201–211 (2016). https://doi.org/10.1007/s10470-015-0683-z

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10470-015-0683-z