Abstract

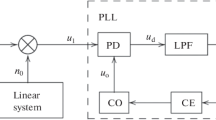

In this paper we study the stability of a phase-locked loop (PLL) in the presence of noise. We represent the noise as Brownian motion and model the circuit as a nonlinear stochastic differential equation, with the noise lumped at the phase detector input. We show that for the PLL, the theory of asymptotics of singular diffusions can be applied and we use this theory to develop a new figure of merit which we call a stability margin. The stability margin provides easily computable bounds on the acceptable noise levels for which stability is guaranteed. Through simulation, we show that such a sufficient bound provides a realistic prediction for PLL stability.

Similar content being viewed by others

Notes

Singular diffusion simply means that the matrix valued function \(\sigma : {\mathbb R}^k \rightarrow {\mathbb R}^{k \times k}\) in (8) is singular, i.e., for all \(X \in {\mathbb R}^k\), \(\det {(\sigma (X))} = 0\).

\(\Vert \cdot \Vert\) can be any vector norm but is taken to be the Euclidean norm in this paper.

The circuit was simulated in MATALB® using the SDEtools library [15].

References

Best, R. E. (1993). Phase-locked loops: Theory, design and applications (6th ed.). New York: McGraw Hill.

Shu, Z., Lee, K., & Leung, B. H. (2004). A 2.4-GHz ring-oscillator-based CMOS frequency synthesizer with a fractional divider dual-PLL architecture. IEEE Journal of Solid-State Circuits, 39(3), 452–462.

Ryu, S., Yeo, H., Lee, Y., Son, S., & Kim, J. (2014). A 9.2 GHz digital phase-locked loop with peaking-free transfer function. IEEE Journal of Solid-State Circuits, 49(8), 1773–1784.

Sai, A., Kobayashi, Y., Saigusa, S., Watanabe, O., & Itakura, T. (2012). A digitally stabilized type-III PLL using ring VCO with 1.01psrms integrated jitter in 65nm CMOS. In 2012 IEEE International Solid-State Circuits Conference Digest of Technical Papers (ISSCC).

Ali, W.E., Hedayat, C., & Hangmann, C. (2013). Simulative characterization of the stability for second order voltage switched CP-PLL. In 2013 IEEE 56th International Midwest Symposium on Circuits and Systems (MWSCAS) (pp. 153–156).

Song, Y., Fu, H., Yu, H. & Shi G. (2013). Stable backward reachability correction for PLL verification with consideration of environmental noise induced jitter. In 18th Asia and South Pacific Design Automation Conference (ASP-DAC) (pp. 755–760).

Mehrotra, A. (2002). Noise analysis of phase-locked loops. IEEE Transactions on Circuits and Systems—I, 49(9), 1309–1316.

Gawalwad, B. G., & Sharma, S. N. (2013) On a perturbed phase-locked loop system: A simple physical model. In 2013 IEEE International Conference on Control Applications (CCA) (pp. 430–436).

Bhattacharya, R. N., & Waymire, E. C. (1990). Stochastic processes with applications (Vol. 61). Philadelphia, PA: SIAM.

Abramovitch, D. (1990). Lyapunov resdesign of analog phase-lock loops. IEEE Transactions on Communications, 38(12), 2197–2202.

Hajimiri, A. (2001). Noise in phase-locked loops. In 2001 Southwest Symposium on Mixed-Signal Design, 2001. SSMSD.

Oksendal, B. (1998). Stochastic differential equations: An introduction with applications. New York: Springer.

Has’minskiĭ, R. Z. (1980). Stochastic stability of differential equations. Alphen aan den Rijn: Sijthoff & Noordhoff.

Wonham, W. (1985). Linear multivariable control: A geometric approach (3rd ed.). New York: Springer.

Horchler, A. SDETools, November 2013. [Online]. Available URL:https://github.com/horchler/SDETools/

Acknowledgments

We thank Professor Andrew Heunis for bringing Theorem 1 to our attention.

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Baker, R.J.A., Leung, B. & Nielsen, C. Phase-locked loop stability based on stochastic bounds. Analog Integr Circ Sig Process 85, 323–333 (2015). https://doi.org/10.1007/s10470-015-0606-z

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10470-015-0606-z