Abstract

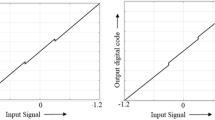

Two digital calibration techniques to linearize the residue amplifier in pipelined SAR ADCs are presented. The proposed techniques utilize a single, one-bit pseudorandom noise (PN) to simultaneously identify all coefficients of a correction polynomial. Behavioral simulation results demonstrate the effectiveness of the two proposed techniques, in which the SNDR and SFDR of a 12-bit pipelined SAR ADC are improved from 54 and 69 dB to 72 and 100 dB, respectively. Some circuit design details are included for the PN injection circuit as well as the digital calibration logic.

Similar content being viewed by others

References

Liu, W, Huang, P., & Chiu, Y., (2010). A 12b 22.5/45MS/s 3.0 mW 0.059 mm2 CMOS SAR ADC achieving over 90 dB SFDR. In IEEE International Solid-State Circuits Conference (ISSCC), Digest of Technical Papers (pp. 380–381).

Lee, C. C., & Flynn, M. P. (2011). A SAR-assisted two-stage pipeline ADC. IEEE Journal of Solid-State Circuits, 46(4), 859–869.

Furuta, M, Nozawa, M., & Itakura, T. (2010). A 0.06 mm2 8.9b ENOB 40MS/s pipelined SAR ADC in 65 nm CMOS. In IEEE International Solid-State Circuits Conference (ISSCC), Digest of Technical Papers (pp. 382–383).

Chiu, Y., Tsang, C. W., Nikolic, B., & Gray, P. R. (2004). Least mean square adaptive digital background calibration of pipelined analog-to-digital converters. IEEE Transactions on Circuits and Systems—Part I, 51(1), 38–46.

McNeill, J., Coln, M. C. W., & Larivee, B. J. (2005). Split ADC architecture for deterministic digital background calibration of a 16-bit 1-MS/s ADC. IEEE Journal of Solid-State Circuits, 40(12), 2437–2445.

Ahmed, I., & Johns, D. A. (2007). An 11-bit 45MS/s pipelined ADC with rapid calibration of DAC errors in a multi-bit pipeline stage. In 33rd IEEE European Solid-State Circuits Conference (ESSCIRC) (pp. 147–150).

Panigada, A., & Galton, I. (2009). A 130 mW 100 MS/s pipelined ADC with 69 dB SNDR enabled by digital harmonic distortion correction. IEEE Journal of Solid-State Circuits, 44(12), 3314–3328.

Yang, W., et al. (2001). A 3-V 340-mW 14-b 75-Msample/s CMOS ADC with 85-dB SFDR at Nyquist input. IEEE Journal of Solid-State Circuits, 36(12), 1931–1936.

Herault, J., & Jutten, C. (1986). Space or time adaptive signal processing by neural network models. In Proceedings of AIP Conference (Vol. 151, p. 206).

Jutten, & Herault, J. (1991). Blind separation of sources, part I: An adaptive algorithm based on neuromimetic architecture. Signal Processing, 24(1), 1–10.

Liu, W., Huang, P., & Chiu, Y. (2012). A 12-bit 50-MS/s 3.3-mW SAR ADC with background digital calibration. In Proceedings of IEEE Custom Integrated Circuits Conference (CICC) (pp. 1–4).

Lee, S. C., & Chiu, Y. (2014). A 15-MHz bandwidth 1-0 MASH ∑∆ ADC with nonlinear memory error calibration achieving 85-dBc SFDR. IEEE Journal of Solid-State Circuits, 49(3), 695–707.

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Zhou, Y., Chiu, Y. Digital calibration of inter-stage nonlinear errors in pipelined SAR ADCs. Analog Integr Circ Sig Process 82, 533–542 (2015). https://doi.org/10.1007/s10470-015-0493-3

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10470-015-0493-3