Abstract

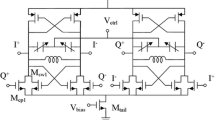

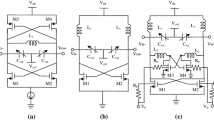

An LC-tank quadrature voltage-controlled oscillator (QVCO) is proposed to achieve frequency-band reconfigurability and low phase noise. In this work, phase noise contributed by the 1/f noise of coupling transistors and tail transistors is noticeably reduced when series coupling and switched biasing techniques are simultaneously adopted. The proposed QVCO was implemented in 0.25-μm triple-well CMOS process for K-PCS and WCDMA bands. Measured results showed a phase noise of −117 dBc/Hz at an offset of 1 MHz and a phase-noise figure-of-merit of −172 dBc/Hz while consuming 8.13 mA from a 2-V power supply.

Similar content being viewed by others

References

Zolfaghari, A., & Razavi, B. (2003). A low-power 2.4 GHz transmitter/receiver CMOS IC. IEEE Journal of Solid-State Circuit, 38(2), 176–183.

Rofougaran, A., Rael, J., Rofougaran, M., & Abidi, A. (1996). A 900-MHz CMOS LC-oscillator with quadrature outputs. ISSCC Digest of Technical Papers, 43(2), 392–393.

Andreani, P. (2002). A 2 GHz, 17 % tuning range quadrature CMOS VCO with high figure-of -merit and 0.6° phase error. In Proc. ESSCIRC, pp. 815–818.

Boon, C. C., Do, M. A., Yeo, K. S., Ma, J. G., & Zhang, X. L. (2004). RF CMOS low-phase-noise LC oscillator through memory reduction tail transistor. IEEE Transactions on Circuits and Systems II: Express Briefs, 51(2), 85–90.

Andreani, P., Bonfanti, A., Romano, L., & Samori, C. (2002). Analysis and design of a 1.8-GHz CMOS LC quadrature VCO. IEEE Journal of Solid-State Circuit, 37(12), 1737–1747.

Klumperink, E. A. M., Gierkink, S. L. J., van derWel, A. P., & Nauta, B. (2000). Reducing MOSFET 1/f noise and power consumption by switched biasing. IEEE Journal of Solid-State Circuit, 35(7), 994–1001.

Gierkink, S. L. J., Klumperink, E. A. M., van derWel, A. P., Hoogzaad, G., van Tuijl, E., & Nauta, B. (1999). Intrinsic 1/f device noise reduction and its effect on phase noise in CMOS ring oscillators. IEEE Journal of Solid-State Circuit, 34(7), 1022–1025.

Shin, H. C., Xu, Z., & Chang, M. F. (2003). A 1.8-V 6/9-GHz reconfigurable dual-band quadrature LC VCO in SiGe BiCMOS technology. IEEE Journal of Solid-State Circuit, 38(6), 1028–1032.

Kim, J.H., & Yoo, H.J. (2005). A dual/wide band quadrature VCO with programmable LC tank for quad-band direct conversion WCDMA/WLAN receiver. In Proc. ICCE, pp. 301–302.

Acknowledgments

This work (No. 2012-2006441) was supported by Basic Science Research Program through the NRF grant funded by the MEST.

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Chang, HJ., Kim, KW., Park, JH. et al. Dual-band low-phase-noise LC-QVCO using series coupling and switched biasing techniques. Analog Integr Circ Sig Process 73, 955–960 (2012). https://doi.org/10.1007/s10470-012-9903-y

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10470-012-9903-y