Abstract

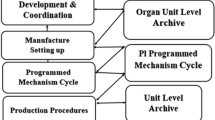

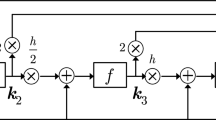

In this paper, we propose new architectures for FPGA-implementation of a dynamic neural network power amplifier behavioral modeling. The real-valued time-delay neural network (RVTDNN) and the backpropagation (BP) learning algorithm were implemented on FPGA using Xilinx system generator for DSP and the Virtex-6 FPGA ML605 evaluation kit. Different RVTDNN architectures are proposed for various values of the number of hidden neurons, the activation function resolution, and the fixed-point data format. These architectures are evaluated and compared in terms of modeling performances and resource utilization using 16-QAM modulated test signal.

Similar content being viewed by others

References

Zhu, A., Pedro, J., & Brazil, T. (2006). Dynamic deviation reduction-based Volterra behavioral modeling of RF power amplifiers. IEEE Transactions on Microwave Theory and Techniques, 54 (12), 4323–4332.

Ku, H., & Kenney, J.S. (2003). Behavioral modeling of nonlinear RF power amplifiers considering memory effects. IEEE Transactions on Microwave Theory and Techniques, 51(12), 2495–2504.

Cao, Y., Chen, X., & Wang, G. (2009). Dynamic behavioral modeling of nonlinear microwave devices using real-time recurrent neural network. IEEE Transactions on Electron Devices, 56(5), 1020–1026.

Liu, T., Boumaiza, S., & Ghannouchi, F. M. (2004). Dynamic behavioral modeling of 3G power amplifiers using real-valued time-delay neural networks. IEEE Transactions on Microwave Theory and Techniques, 52(3), 1025–1033.

Mkadem, F., & Boumaiza, S. (2011). Physically inspired neural network model for RF power amplifier behavioral modeling and digital predistortion. IEEE Transactions on Microwave Theory and Techniques, 59(4), 913–923.

Rawat, M., Rawat, K., & Ghannouchi, F. M. (2010) Adaptive digital predistortion of wireless power amplifiers/transmitters using dynamic real-valued focused time-delay line neural networks. IEEE Transactions on Microwave Theory and Techniques, 58(1), 95–104.

Lee, K. C., & Gardner, P. (2006). Adaptive neuro-fuzzy inference system ANFIS digital predistorter for RF power amplifier linearization. IEEE Transactions on Vehicular Technology, 55 (1), 43–51.

Cybenko, G. (1989). Approximation by superpositions of a sigmoidal function. Mathematics of Control, Signals, and Systems, 2(4), 303–314.

Hornik, K., Stinchcombe, M., & White, H. (1989). Multilayer feedforward networks are universal approximators. Neural Networks, 2(5), 359–366.

Chen, Q., Chan, Y. W., & Worden, K. (2003). Structural fault diagnosis and isolation using neural networks based on response-only data. Computers & Structures, 81(22–23), 2165–2172.

Bahoura, M., & Park, C.-W. (2011). FPGA-implementation of an adaptive neural network for RF power amplifier modeling. In: 9th IEEE Iiternational NEWCAS conference, Bordeaux, France, June 2011 (pp. 29–32).

Cherubini, D., Fanni, A., Montisci, A., & Testoni, P. (2005). A fast algorithm for inversion of MLP networks in design problems. COMPEL-The International Journal for Computation and Mathematics in Electrical and Electronic Engineering, 24(3), 906–920.

Haykin, S. (1999). Neural networks: A comprehensive foundation (2nd edn). Upper Saddle River, NJ: Prentice-Hall.

Saleh, A. A. M. (1981). Frequency-independent and frequency-dependent nonlinear models of TWT amplifiers. IEEE Transactions on Communications, 29(11), 1715–1720.

Bastos, J. L., Figueroa, H. P., & Monti, A. (2006). FPGA implementation of neural network-based controllers for power electronics applications. In Twenty-first annual IEEE applied power electronics conf. and Exp., 2006. APEC ’06 (pp. 1443–1448).

Bahoura, M., & Ezzaidi, H. (2011). FPGA-implementation of parallel and sequential architectures for adaptive noise cancelation. Circuits, Systems, and Signal Processing, 30(6), 1521–1548.

Bahoura, M., & Park, C.-W. (2011). FPGA-implementation of high-speed MLP neural network. In 18th IEEE international conference on electronics, circuits, and systems, ICECS 2011, Beirut, Lebanon, Dec 2011 (pp. 426–429).

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Bahoura, M., Park, CW. FPGA-implementation of dynamic time delay neural network for power amplifier behavioral modeling. Analog Integr Circ Sig Process 73, 819–828 (2012). https://doi.org/10.1007/s10470-012-9857-0

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10470-012-9857-0