Abstract

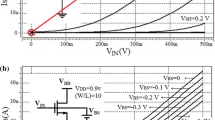

Leakage power dissipation is the dominant contributor of total power dissipation in nanoscale complementary metal oxide semiconductor (CMOS) integrated circuits. CMOS technology scaling demands for a reduced power supply, low threshold voltage, high transistor density and reduced oxide thickness, which has led to significant increase in leakage power especially during standby mode. Here in this paper, at first we review some of the existing techniques for leakage minimization and pointed out their merits and shortcomings. We then propose a novel transistor level approach called leakage control NMOS transistor (LCNT) for leakage minimization. The proposed technique inserts two leakage control transistors (all N-type) within a standard CMOS logic circuit. The gate terminal of the leakage control transistors are connected with the drain of the pull-up transistors. Performance of the proposed technique is investigated in terms of area, power, delay, and power-delay product applying on some basic gates and benchmark circuits. The performance metrics of the proposed LCNT are then compared with other existing techniques. Extensive SPICE simulations were carried out using 32 nm predictive technology model. Simulation results indicate that the proposed technique is quite efficient in minimizing the leakage power which is found out to be 48.4 %.

Similar content being viewed by others

References

Butzen PF, da Rosa Jr LS, Chiappetta Filho EJ, Reis AI, Ribas RP (2010) Standby power consumption estimation by interacting leakage current mechanisms in nanoscaled CMOS digital circuits. Microelectron J 41(4):247–255

Chin P, Zukowski CA, Gristede GD, Kosonocky SV (2005) Characterization of logic circuit techniques and optimization for high-leakage CMOS technologies. Integr VLSI J 38(3):491–504

Drake AJ, Zamdmer N, Nowka KJ, Brown RB (2003) Analysis of the impact of gate body signal phase on DTMOS Inverters in 0.13 µm PD-SOI. In: IEEE international SOI conference, pp 99–100

Ekekwe N, Etienne-Cummings R (2006) Power dissipation sources and possible control techniques in ultra deep submicron CMOS technologies. Microelectron J 37(9):851–860

Faraji R, Hamid Reza N, Majid Rahimi N, Mohammad A (2013) New SRAM design using body bias technique for low-power and high-speed applications. Int J Circuit Theory Appl 42(11):1189–1202

Hanchate N, Ranganathan N (2004) Lector: a technique for leakage reduction in CMOS circuits. IEEE Trans. VLSI Integr Syst 12(2):196–205

Hun K, Mooney VJ (2006) Sleepy keeper: a new approach to low-leakage power VLSI design. In: Proc. IFIP international conference on very large scale integration, pp 367–372

International Technology Roadmap for Semiconductor (2009). http://www.itrs.net

Kao J, Chandrakasan A (2000) Dual-threshold voltage techniques forlow-power digital circuits. IEEE J Solid-State Circuit 35(7):1009–1018

Kao J, Chandrakasan A (2001) MTCMOS sequential circuits. In: Proceedings of European solid-state circuits conference, pp 332–335

Katrue S, Kudithipudi D(2008) GALEOR: leakage reduction for CMOS circuits. In: 15th IEEE international conference on electronics, circuits and systems, pp 574–577

Kuroda T, Fujita T, Mita S, Nagamatsu T, Yoshioka S, Suzuki K, Sano F, Norishima M, Murota M, Kako M, Kinugawa M, Kakumu M, Sakurai T (1996) A 0.9 V, 150 MHz, 10 mW, 4 mm2, 2-D discrete cosine transform core processor with variable threshold-voltage (VT) scheme. IEEE J Solid Circuit 31(11):1770–1779

Mutoh S, Douseki T, Matsuya Y, Aoki T, Shigematsu S, Yamada J (1995) 1 V power supply high-speed digital circuit technology with multithreshold-voltage CMOS. IEEE J Solid-State Circuit 30(8):847–854

Narendra S, Borkar S, De V, Antoniadis D, Chandrakasan AP (2001) Scaling of stack effect and its application for leakage reduction. In: Proc. IEEE ISLPLED, pp 195–200

Narendran S, Borkar S, De V, Antoniadisn D, Chandrakasann A (2001). In: Proceedings ISLPED, pp 195–200

Park JC, Mooney VJ (2006) Sleepy stack leakage reduction. IEEE Trans VLSI Syst 14(11):1250–1263

Park JC, Mooney III VJ, Pfeiffenberger P (2004) Sleepy stack reduction of leakage power. In: Proceeding of the international workshop on power and timing modeling, optimization and simulation, pp 148–158

Roy K, Prasad SC, Horowitz MA (2000) Low-power CMOS VLSI circuit design, chapter 5. Wiley, New York, p 214–219

Sayed A, Al Asaad H (2006) A new low power high performance flip-flop. In: 49th IEEE international midwest symposium on circuits and systems, pp 723–726

Sharma VK, Pattanaik M, Raj B (2014) ONOFIC approach: low power high speed nanoscale VLSI circuits design. Int J Electron 101(1):61–73 (Taylor and Francis)

Sharma VK, Pattanaik M, Raj B (2015) INDEP approach for leakage reduction in nanoscale CMOS circuits. Int J Electron 102(2):200–215 (Taylor and Francis)

Sirichotiyakul S, Edwards T, Oh C, Panda R, Blaauw D (2002) Duet: an accurate leakage estimation and optimization tool for dual-V circuits. IEEE Trans VLSI Syst 10(2):79–90

Tsui CY, Au RYC, Choi RYK (2008) Minimizing the dynamic and sub-threshold leakage power consumption using least leakage vector-assisted technology mapping. Integr VLSI J 41(1):76–86

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Lorenzo, R., Chaudhury, S. LCNT-an approach to minimize leakage power in CMOS integrated circuits. Microsyst Technol 23, 4245–4253 (2017). https://doi.org/10.1007/s00542-016-2996-y

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s00542-016-2996-y