Abstract.

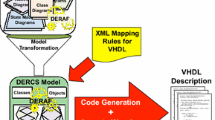

This paper details a new object-oriented methodology that permits a unified modelling language (UML) behavioural representation of analogue circuits at system level. The proposed method demonstrates a novel approach to the problem of behavioural representation of an analogue topology, by constructing a consistent set of rules for automated mapping of the UML model to a VHDL-AMS specification. The VHDL-AMS specification enables behavioural simulation of the UML model and the methodology is validated using an analogue subsystem level application.

Similar content being viewed by others

Author information

Authors and Affiliations

Corresponding author

Additional information

Correspondence and offprint request to: C. T. Carr, Intelligent Systems Engineering Laboratory, University of Ulster, Magee Campus, Northland Rd, Derry, Northern Ireland, BT48 7JL, UK.

Received May 2002 Accepted in revised form September 2003 by C. Delgado Kloos

Rights and permissions

About this article

Cite this article

Carr, C., McGinnity, T. & McDaid, L. Integration of UML and VHDL-AMS for analogue system modelling. Formal Aspects of Computing 16, 80–94 (2004). https://doi.org/10.1007/s00165-003-0027-0

Published:

Issue Date:

DOI: https://doi.org/10.1007/s00165-003-0027-0