Abstract

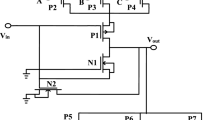

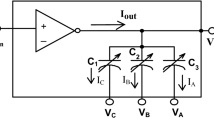

Digitally controlled oscillators are the main cores in all-digital phase-locked loops (ADPLL), which are important for determining the range of frequency and power consumption in ADPLLs. In the conventional digitally controlled oscillator (DCO) designs, one single band of operation is assigned to the DCO. The following paper presents a new approach in the design of DCOs, which works in dual-band and wide-band modes with a control unit. In dual-band mode, the DCO works in two different ranges of frequencies simultaneously via digital control bits. The wide-band DCO (WBDCO) works in one wider range of frequencies consecutively. It seems that in the wide-band DCO, the gap width for the dual-band DCO (DBDCO) is zero. The previously mentioned designs allow the designer to have standard frequencies with the help of direct or multiplied frequencies. So, we can have a trade-off between power and performance. This means that we can have low power consumption in low-frequency applications and vice versa. The proposed designs are based on using digitally controlled capacitors, current starving gates and Schmitt triggers in critical points of the DCO loop, while preserving coarse and fine tunings. The non-delay linearity factors are clearly investigated and resolved with the use of a new combined control unit. The simulations of the proposed designs are performed in Hspice with a voltage of \(\mathrm{VDD}=1.8\) v in 180 nm CMOS technology for 64- and 128-bit input coarse codes. Our simulation and evaluation results showed that in the dual-band DCO, a 14.8 ps jitter was calculated at 134 MHz with 1.2131 mW power consumption, while in the wide band with overlap mode, a 68.7 ps jitter was measured at 184.61 MHz with 1.604 mW power consumption. Our designs are proper for reconfigurable and multi-standard ADPLL designs.

Similar content being viewed by others

References

W. Altabban, P. Desgreys, H. Petit, K. Ben Kalaia, L.R. du Roscoat, Merged digitally controlled oscillator and time to digital converter for TV band ADPLL. in Proceedings of 2010 IEEE International Symposium on Circuits and Systems (ISCAS), 2010, pp. 1987–1990

D. Banerjee, PLL Performance Simulation and Design (Dog Ear Publishing, Indianapolis, 2006)

P.-L. Chen, C.-C. Chung, C.-Y. Lee, A portable digitally controlled oscillator using novel varactors. IEEE Trans. Circuits Syst. II: Express Briefs 52, 233–237 (2005)

T.-D. Chiueh, J.-B. Yang, W. Jen-Shi, Design and implementation of a low-voltage fast-switching mixed-signal-controlled frequency synthesizer. IEEE Trans. Circuits Syst. II: Analog. Digit. Signal Process. 48, 961–971 (2001)

J. Dunning, G. Garica, J. Lunberg, E. Nuckolls, An all-digital phase-locked loop with 50-cycle lock time suitable for high-performance microprocessors. IEICE Trans. Electron. 78, 660–670 (1995)

M.E.S. Elrabaa, A portable high-frequency digitally controlled oscillator (DCO). Integr. VLSI J. 47, 339–346 (2014)

W. Jiang, ADPLL Design for WiMAX, PhD Thesis of the Delft University of Technology (2011)

W. Jiang, A. Tavakol, P. Effendrik, M. van de Gevel, F. Verwaal, R.B. Staszewski, Design of ADPLL System for WiMAX Applications in 40-nm CMOS. in 19th IEEE International Conference on Electronics, Circuits and Systems (ICECS), 2012, pp. 73–76

G. Jovanovic, M. Stojčev, Z. Stamenkovic, A CMOS Voltage Controlled Ring Oscillator with Improved Frequency Stability, Scientific Publications of the State University of Novi Pazar, Series A: Applied Mathematics, Informatics and mechanics 2, (2010), 1–9

A. Kavala, W. Bae, S. Kim, G.-M. Hong, H. Chi, S. Kim, D.-K. Jeong, A PVT-compensated 2.2–3.0 GHz digitally controlled oscillator for all-digital PLL. J. Semicond. Tech. Sci. 14(4), 484–494 (2014)

M. Kumar, S.K. Arya, P. Sujata, Timsi, Low power CMOS digitally controlled oscillator, Int. J. Eng. Technol. 2(4), 240–244 (2010)

A.V.M.P. Kumar, T.K. Kumar, V.G.P. Kumar, Low-power digitally controlled oscillator (DCO) for SoC applications. IJECCE 4, 474–477 (2013)

H. Li, B. Zhang, P. Luo, J. Liu, Z. Li, A compact ADPLL based on symmetrical binary frequency searching with the same circuit. Int. J. Electron. 102(3), 462–475 (2015)

M.-L. Lina, S.-C. Huang, J.-C. Liu, Digital-only PLL with adaptive search step. Int. J. Electron. 101(6), 865–876 (2014)

N.E. Majd, M. Lotfizad, A. Abadian, M.B. Ghaznavi-Ghoushchi, An ultra low-power digitally controlled oscillator using novel Schmitt-trigger based hysteresis delay cells. IEICE Electron. Express 8, 589–595 (2011)

N.E. Majd, M. Lotfizad, A Novel Low Power Digitally Controlled Oscillator with Improved linear Operating Range (Scientific Research Publishing in Circuits and Systems (CS), Inc., USA, 2011), pp. 129–134

C. Maxey, S. Raman, k-Band differential and quadrature digitally-controlled oscillator designs in SiGe BiCMOS technology. in \(14th\) IEEE Topical Meeting on Silicon Monolithic Integrated Circuits in Rf Systems (SiRF), 2014, pp. 110–112

A. Mazzanti, P. Uggetti, R. Battagila, F. Svelto, Analysis and design of a dual-band reconfigurable VCO. in 11th IEEE International Conference on Electronics, Circuits and Systems, ICECS 2004, 2004, pp. 37–40

B. Narendran, R. Parameshwaran, Comparison of various optimized architectures of DCO for ADPLL. Contemp. Eng. Sci. 7(9), 419–425 (2014)

P. Nugroho, R.K. Pokharel, A. Anand, R. Hashimura, G. Zhang, R. Dong, H. Kanaya, K. Yoshida, A low power 8-bit digitally controlled CMOS ring oscillator. 7th European in Microwave Integrated Circuits Conference (EuMIC), 2012, pp. 504–507

T. Olsson, P. Nilsson, A digitally controlled PLL for SoC applications. IEEE J. Solid-State Circuit 39, 751–760 (2004)

V. Pedroni, Low-voltage high-speed Schmitt trigger and compact window comparator. Electron. Lett. 41, 1213–1214 (2005)

B. Razavi, Design of analog CMOS integrated circuits (McGraw-Hill, New York, 2002)

S.-Y. Seo, J.-H. Chun, Y.-H. Jun, S. Kim, K.-W. Kwon, A digitally controlled oscillator with wide frequency range and low supply sensitivity. IEEE Trans. Circuits Syst. II: Express Briefs 58, 632–636 (2011)

R.B. Staszewski, P.L. Balsara, All-digital PLL with ultra fast settling. IEEE Trans. Circuits Syst. II: Express Briefs 54, 181–185 (2007)

M.-C. Su, S.-J. Jou, Digitally-controlled cell-based oscillator with multi-phase differential outputs. in 9th IEEE International Conference on ASIC (ASICON), 2011, pp. 610–613

C. Zhang, Techniques for low power analog, digital and mixed signal CMOS integrated circuit design, PhD Thesis of the Louisiana State University (2005)

J. Zhao, Y.B. Kim, A 12-bit digitally controlled oscillator with low power consumption. in 51st Midwest Symposium in Circuits and Systems on 2008, MWSCAS 2008, 2008, pp. 370–373

J. Zhao, Y.B. Kim, A low-power digitally controlled oscillator for all-digital phase-locked loops. VLSI Des. 2010(2), 1–11 (2010)

Acknowledgments

The authors wish to thank the following persons for their helps: Dr. Mohsen Jalali of Shahed university, Saied Souri of Qazvin University, Mahmoud Pourbafrani of Esfahan university, Mahshid Rahimi of Shahab Danesh University, Arash Abadian of Tehran University, Naser Erfani-Majd of Amirkabir University of Technology, Saberi Moqadam, Somayye Badvi, Masuomeh Rahimi and Somayye Yousefi. The authors wish to thank anonymous reviewers for their fruitful comments and questions during the review phase. The first author specially wishes to thank her beloved parents for their support and encouragements during the development of this work.

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Souri, M., Ghaznavi-Ghoushchi, M.B. Two Efficient Dual-Band and Wide-Band Low-Power DCO Designs Using Current Starving Gates, DCV and Reconfigurable Schmitt Triggers in 180 nm. Circuits Syst Signal Process 35, 1481–1505 (2016). https://doi.org/10.1007/s00034-015-0127-0

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s00034-015-0127-0