Abstract

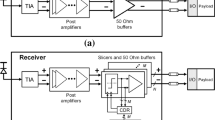

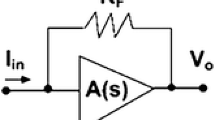

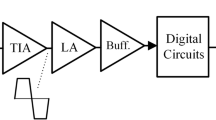

This paper presents the design of a framework for the optimization of a low-power, low-noise, broadband transimpedance amplifier to be used in a fiber optic transceiver. The design is implemented using a 180 nm six-metal-layer digital CMOS process with a 1.8V supply. The performances achieved are a gain of \(78.34\,\hbox { dB}\Omega \), a bandwidth of 2.21 GHz, an input referred current noise of \(11.91\,\hbox { pA/Hz}^{1/2}\), and a power dissipation of 13.5 mW.

Similar content being viewed by others

References

T.C. Carusone, D.A. Johns, K.W. Martin, Analog Integrated Circuits, 2nd edn. (Wiley, Hoboken, 2011)

Y.-H. Kim, S.-S. Lee, \(\text{ A } 72\,\text{ dB }\Omega \) 11.43 mA novel CMOS regulated cascode TIA for 3.125 Gb/s optical communications, in IEEE International SOC Conference, pp. 68–72 (2013)

H.M. Lavasani et al., A \(76\,\text{ db }\Omega \) 1.7 GHz \(0.18\upmu \text{ m }\) CMOS tunable TIA using broadband current pre-amplifier for high frequency lateral MEMS oscillators. IEEE J. Solid State Circuits 44(1), 224–235 (2011)

C.-F. Liao, S.-I. Liu, 40 Gb/s transimpedance-AGC amplifier and CDR circuit for broadband data receivers in 90 nm CMOS. IEEE J. Solid State Circuits 43(3), 642–655 (2008)

P. Marconcini, The role of the choice of the physical model in the optimization of nanoelectronic device simulators. Int. J. Circuits Syst. Signal Process. 7(3), 173–180 (2013)

B. Murmann, in Analysis and Design of Elementary MOS Amplifier Stages (NTS Press, 2013)

S.M. Park, H.-J. Yoo, 1.25-Gb/s regulated cascode CMOS transimpedance amplifier for gigabit ethernet applications. IEEE J. Solid State Circuits 39(1), 112–121 (2004)

B. Razavi, Design of Integrated Circuits for Optical Communications, 2nd edn. (Wiley, Hoboken, New Jersey, 2012)

J. Salvia, P. Lajevardi, M. Hekmat, B. Murmann, A \(56\,\text{ M }\Omega \) CMOS TIA for MEMS applications, in IEEE Custom Integrated Circuits Conference, pp. 199–202 (2009)

F. Silveira, D. Flandre, P.G.A. Jesper, A gm/ID based methodology for the design of CMOS analog circuits and its application to the synthsis of a silicon-on-insulator micropower OTA. IEEE J. Solid State Circuits 31(9), 1314–1319 (1996)

C. Talarico, G. Agrawal, J. Wang-Roveda, Design optimization of a TIA for high speed data applications using gm/ID based methodology, in Proceedings of the 18th International Conference on Circuits: Advances in Robotics, Mechatronics and Circuits, EUROPMENT, Santorini, Greece, pp. 40–45 (2014)

C. Talarico, J. Sun, P. Gupta, J. Wang, A new framework for the design of analog blocks using conic uncertainty budgeting. Int. J. Circuits Syst. Signal Process. 7(3), 143–150 (2013)

M.-J. Wu, Y.-H. Lee, Y.-Y. Huang, Y.-M. Mu, J.-T. Yang, A CMOS multi-band low noise amplifier using high-Q active inductors. Int. J. Circuits Syst. Signal Process. 2(2), 199–202 (2007)

D.S. Yen Nguyen, Q.H. Duong, T.A. Phan, H.H. Nguyen, X. Yu, S.-G. Lee, A high linearity, low noise, and high gain transimpedance amplifier (TIA), in IEEE International Conference on Solid-State and Integrated Circuit Technology, pp. 1553–1555 (2006)

Author information

Authors and Affiliations

Corresponding author

Additional information

Part of the present paper was presented at the 18th International Conference on Circuits: Advances in Robotics, Mechatronics and Circuits, EUROPMENT, Santorini, Greece (2014) [11].

Rights and permissions

About this article

Cite this article

Talarico, C., Agrawal, G., Wang-Roveda, J. et al. Design Optimization of a Transimpedance Amplifier for a Fiber Optic Receiver. Circuits Syst Signal Process 34, 2785–2800 (2015). https://doi.org/10.1007/s00034-015-0002-z

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s00034-015-0002-z