Abstract

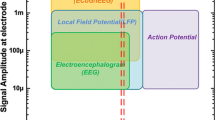

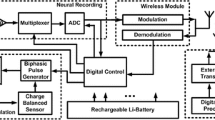

This paper presents an ultra-low power and small area analog front-end for an implantable multichannel neural signal recording and stimulation interface, to be used in wirelessly powered implantable Brain-Machine Interfaces. For a given functionality and performance, area, power, and noise-response are the three critical parameters that define the suitability of a design for implantation. The three main components of a typical neural implant are the analog front-end, the digital processor, and the wireless data and power transceiver. Among them, neural front-end is the most power and area hungry module. This paper presents an 8-channel analog front-end prototype for simultaneous recording and stimulation, employing a novel architecture which significantly improves power and area consumption of the chip over current state of the art. In contrast to published architectures, the multichannel recording path is centered on a single super-performing tunable gain-bandwidth amplifier instead of employing a separate stand-alone amplifier for each electrode. The resulting circuitry requires smaller area and less power compared to all previously published designs. Designed in 0.5 \(\upmu \)m CMOS with VDD of 1.8 V, the 8-channel recording path consume a total of 77 \(\upmu \)W of power and a net area of 0.24 mm\(^{2}\), allowing scalability to a high channel count. The stimulation path utilizes 8 stimulators, each employing an 8-bit multibias DAC with a current amplifier to drive electrode–electrolyte high impedance load. Each stimulator consumes full scale power of 224 \(\upmu \)W and entire stimulation path occupies an area of 0.32 mm\(^{2}\).

Similar content being viewed by others

References

J.N.Y. Aziz, K. Abdelhalim, R. Shulyzki, R. Genov, B.L. Bardakjian, M. Derchansky, D. Serletis, P.L. Carlen, 256-channel neural recording and delta compression microsystem with 3D electrodes. IEEE J. Solid State Circ. 44, 995–1005 (2009)

M.S. Chae, W. Liu, M. Sivaprakasam, Design optimization for integrated neural recording systems. IEEE J. Solid State Circ. 43, 1931–1939 (2008)

T.G. Constandinou, J. Georgiou, C. Toumazou, A Partial-current-steering biphasic stimulation driver for vestibular prostheses. IEEE Trans. Biomed. Circ. Syst. 2, 106–113 (2008)

M. Conti, P. Crippa, S. Orcioni, C. Turchetti, Parametric yield formulation of MOS IC’s affected by mismatch effect. IEEE Trans. Comput. Aided Des. Integr. Circ. Syst. 18, 582–596 (1999)

P. Crippa, C. Turchetti, M. Conti, A statistical methodology for the design of high-performance CMOS current-steering digital-to-analog converters. IEEE Trans. Comput. Aided Des. Integr. Circ. Syst. 21, 377–394 (2002)

S.C. DeMarco, W. Liu, P.R. Singh, G. Lazzi, M.S. Humayun, An arbitrary waveform stimulus circuit for visual prostheses using a low-area multibias DAC. IEEE J. Solid State Circ. 38, 1679–1690 (2003)

R.R. Harrison, A versatile integrated circuit for the acquisition of biopotentials, in IEEE Custom Integrated Circuits Conference, pp. 115–122 (2007)

E.A. Heming, R. Choo, J.N. Davies, Z.H.T. Kiss, Designing a thalamic somatosensory neural prosthesis: consistency and persistence of percepts evoked by electrical stimulation. IEEE Trans. Neural Syst. Rehab. Eng. 19, 477–482 (2011)

C. Kim, K.D. Wise, A 64-site multi-shank CMOS low-profile neural stimulating probe. IEEE J. Solid State Circ. 31, 1230–1238 (1996)

J. Lee, H.G. Rhew, D. Kipke, M. Flynn, A 64 channel programmable closed-loop deep brain stimulator with 8 channel neural amplifier and logarithmic ADC, in IEEE Symposium on VLSI Circuits, pp. 76–77 (2008)

W. Liu, K. Vichienchom, M. Clements, S.C. DeMarco, C. Hughes, E. McGucken, M.S. Humayun, E. De Juan, J.D. Weiland, R. Greenberg, A neurostimulus chip with telemetry unit for retinal prosthetic device. IEEE J. Solid State Circ. 35, 1487–1497 (2000)

Y.T. Liu, D.Y.C. Lie, W. Hu, T. Nguyen, An ultra-low power CMOS transconductor design with wide input linear range for biomedical applications, in IEEE International Symposium on Circuits and System, pp. 2211–2214 (2012)

V. Majidzadeh, A. Schmid, Y. Leblebici, Energy efficient low noise neural recording amplifier with enhanced noise efficiency factor. IEEE Trans. Biomed. Circ. Syst. 5, 262–271 (2011)

E.M. Maynard, C.T. Nordhausen, R.A. Normann, The utah intra cortical electrode array: a recording structure for potential brain–computer interfaces. Electroencephalogr. Clin. Neurophysiol. 102, 228–239 (1997)

M. Ortmanns, N. Unger, A. Rocke, M. Gehrke, H.J. Tiedtke, A 0.1 mm digitally programmable nerve stimulation pad cell with high-voltage capability for a retinal implant, in IEEE International Solid State Circuit Conference, pp. 89–98 (2006)

M.J.M. Pelgrom, Aad.C.J. Duinmaijer, A.P.G. Welbers, Matching properties of MOS transistors. IEEE J. Solid State Circ. 24, 1433–1439 (1989)

B. Razavi, Design of Analog CMOS Integrated Circuits (McGraw Hill, New York, 2001)

S.S. Saberhosseini, A. Zabihian, A.M. Sodagar, Low-noise OTA for neural amplifying applications, in International Caribbean Conference on Devices, Circuits and Systems, pp. 1–4 (2012)

M.D. Scott, B.E. Boser, K.S.J. Pister, An ultralow-energy ADC for smart dust. IEEE J. Solid State Circ. 38, 1123–1129 (2003)

F. Shahrokhi, K. Abdelhalim, D. Serletis, P.L. Carlen, R. Genov, 128-Channel fully differential digital integrated neural recording and stimulation interface. IEEE Trans. Biomed. Circ. Syst. 4, 149–161 (2010)

M.S.J. Steyaert, W.M.C. Sansen, A micropower low-noise monolithic instrumentation amplifier for medical purposes. IEEE J. Solid State Circ. 22, 1163–1168 (1987)

M. Wang, C.E. Saavedra, Very low frequency tunable signal generator for neural and cardiac cell stimulation. Int. J. Electron. 98, 1215–1227 (2011)

W. Wattanapanitch, R. Sarpeshkar, A low-power 32-channel digitally programmable neural recording integrated circuit. IEEE Trans. Biomed. Circ. Syst. 5, 592–602 (2011)

M. Yin, M. Ghovanloo, A low-noise preamplifier with adjustable gain and bandwidth for biopotential recording applications, in IEEE International Symposium on Circuits and Systems, pp. 321–324 (2007)

Acknowledgments

The authors would like to acknowledge technical help by Prof. Andrew Mason and Mr. Yuning Yang from Department of Electrical and Computer Engineering, Michigan State University, East Lansing, USA.

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Rehman, S.U., Kamboh, A.M. A CMOS Micro-power and Area Efficient Neural Recording and Stimulation Front-End for Biomedical Applications. Circuits Syst Signal Process 34, 1725–1746 (2015). https://doi.org/10.1007/s00034-014-9935-x

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s00034-014-9935-x