Abstract

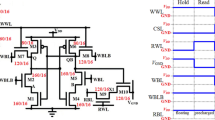

A new memory design with a simple six-transistor memory cell achieves an enhanced read static noise margin. Based on using “pre-equalize” rather than “pre-charge” at the beginning of a read operation, the cross-coupled inverters of the memory cell have a switching threshold close to that of the conventional CMOS inverter circuit, thus achieving both compactness and increased data stability. The proposed can also potentially dramatically decrease power dissipation in conventional memory counterparts. Both simulations and measurements were carried out as proof of concept. The proposed memory hardware techniques are simple to implement and highly practical, making it quite competitive with other currently used methods.

Similar content being viewed by others

References

L. Chang, D.M. Fried, J. Hergenrother, J.W. Sleight, R.H. Dennard, R.K. Montoye, L. Sekaric, S.J. McNab, A.W. Topol, C.D. Adams, K.W. Guarini, W. Haensch, Stable SRAM cell design for the 32 nm node and beyond. in Proceedings of Symposium on VLSI Technology Digest, pp. 128–129 (2005)

Y. Chung, S.W. Shim, Sub-1V embedded SRAM with bit-error immune dual-boosted cell technique. Electron. Lett. 43(3), 157–158 (2007)

D.A. Hodges, H.G. Jackson, R.A. Saleh, Analysis and Design of Digital Integrated Circuits, 3rd edn. (McGraw-Hill, New York, 2003)

K. Kanda, H. Sadaaki, T. Sakurai, 90 % write power-saving SRAM using sense-amplifying memory cell. IEEE J. Solid-State Circ. 39(6), 927–933 (2004)

Z. Liu, V. Kursun, Characterization of a novel nine-transistor SRAM cell. IEEE Trans. VLSI Syst. 16(4), 488–492 (2008)

K. Takeda, Y. Hagihara, Y. Aimoto, M. Nomura, Y. Nakazawa, T. Ishii, H. Kobatake, A read-static-noise-margin-free SRAM cell for low-VDD and high-speed applications. IEEE J. Solid-State Circ. 41(1), 113–121 (2006)

Acknowledgments

This study was supported in part by the National Science Council (NSC), Taiwan under Grant NSC 102-2218-E-182-003-, and by the Ministry of Science and Technology (MOST), Taiwan, under Grant MOST 103-2221-E-182-070-. Additional support was provided by Chang Gung University (CGU) under contracts UERPD2D0011 and UERPD2D0051.

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Gong, CS.A. Investigation of Noise-Margin-Enhanced and Low-Power Memory Techniques for SoC Applications. Circuits Syst Signal Process 34, 1115–1128 (2015). https://doi.org/10.1007/s00034-014-9898-y

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s00034-014-9898-y