Abstract

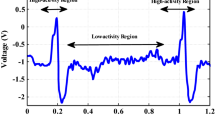

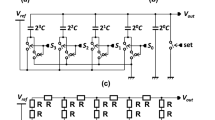

Square-root-domain (SRD) CMOS analog realization of a single cell architecture of the complex Temporal Derivative Cellular Neural Networks (TDCNNs) is introduced in this paper. TDCNN initiates time derivative ‘diffusion’ between CNN cells for non-separable spatiotemporal filtering applications, where the input to the CNN is an image that changes over time. The evaluation of the performance of the complex SRD TDCNN cell has been done using the Cadence Orcad software with TSMC 0.18-μm CMOS process model parameters. The provided simulated results confirm the validity of the theory.

Similar content being viewed by others

References

C. Chao-Ming, L. Chih-Min, C. Ching-Tsan, D.S. Yeung, Hardware implementation of CMAC neural network using FPGA approach, in IEEE International Conference on Machine Learning and Cybernetics, vol. 4 (2007), pp. 2005–2011

H.P. Chen, Y.Z. Liao, W.T. Lee, Tunable mixed-mode OTA-C universal filter. Analog Integr. Circuits Signal Process. 58, 135–141 (2009)

L.O. Chua, L. Yang, Cellular neural networks: theory. IEEE Trans. Circuits Syst. I 35, 1257–1272 (1988)

L.O. Chua, T. Roska, Cellular Neural Networks and Visual Computing (Cambridge University Press, Cambridge, 2002)

L.O. Chua, T. Roska, The CNN paradigm. IEEE Trans. Circuits Syst. I 40, 147–156 (1993)

C.A. De La Cruz-Blas, A.J. Lopez-Martin, A. Carlosena, 1.5 V tunable square root domain filter. Electron. Lett. 40, 213–214 (2004)

C.A. De La Cruz-Blas, A.J. Lopez-Martin, A. Carlosena, Low-voltage nonlinear CMOS transconductors and their application to companding current-mode filters. Analog Integr. Circuits Signal Process. 38, 137–147 (2004)

M. Eskiverli, A. Payne, Square-root domain filter design and performance. Analog Integr. Circuits Signal Process. 22, 231–243 (2000)

S. Espejo, R. Carmona, R. Dominguez-Castro, A. Rodriguez-Vazquez, A CNN universal chip in CMOS technology. Int. J. Circuit Theory Appl. 24, 93–110 (1996)

S. Espejo, R. Carmona, R. Dominguez-Castro, A. Rodriguez-Vazquez, A VLSI-oriented continuous-time CNN model. Int. J. Circuit Theory Appl. 24, 341–356 (1996)

M.D.I. Henry, E.M. Drakakis, A.A. Bharath, On analog networks and mixed-domain spatio-temporal frequency response. IEEE Trans. Circuits Syst. I 55, 284–297 (2008)

M.D.I. Henry, E.M. Drakakis, A.A. Bharath, Preliminary results from an analog implementation of first-order TDCNN dynamics. Int. J. Circuit Theory Appl. 39, 665–678 (2011)

M.D.I. Henry, E.M. Drakakis, A.A. Bharath, Synthesis of nonseparable 3D spatiotemporal bandpass filters on analog networks. IEEE Trans. Circuits Syst. I 55, 284–297 (2008)

J.J. Hopfield, Neural networks and physical systems with emergent computational abilities. Proc. Natl. Acad. Sci. USA 79, 2554–2558 (1982)

P. Kinget, M. Steyaert, An analog parallel array processor for real-time sensor signal processing, in Proc. IEEE Int. Solid-State Circuits Conf., San Francisco, CA, USA (1996), pp. 92–93

V. Lanza, F. Corinto, M. Gilli, P.P. Civalleri, Analysis of nonlinear oscillatory network dynamics via time-varying amplitude and phase variables. Int. J. Circuit Theory Appl. 35, 623–644 (2007)

K.W. Martin, Complex signal processing is not complex. IEEE Trans. Circuits Syst. I 51, 1823–1836 (2004)

P.B.L. Meijer, Neural network applications in device and subcircuit modeling for circuit simulation. PhD thesis, Eindhoven University (1996)

G.E. Paxienza, X. Ponce-Garcia, M. Balsi, X. Vilasis-Cardona, Robot vision with cellular neural networks: a practical implementation of new algorithms. Int. J. Circuit Theory Appl. 35, 449–462 (2006)

C. Psychalinos, S. Vlassis, A systematic design procedure for square-root domain circuits based on the signal flow graph approach. IEEE Trans. Circuits Syst. I 49, 1702–1712 (2002)

C. Psychalinos, Square-root domain wave filters. Int. J. Circuit Theory Appl. 35, 131–148 (2007)

C. Psychalinos, Design of square-root domain filters by substituting the passive elements of the prototype filter by their equivalents. Int. J. Circuit Theory Appl. 36, 185–204 (2008)

A. Rodriguez Vazquez, S. Espejo, R. Dominguez-Castro, R. Carmona, E. Roca, Mixed-signal CNN array chips for image processing. Proc. SPIE A2950, 218–229 (1996)

E. Saatci, V. Tavsanoglu, Fingerprint image enhancement using CNN filtering techniques. Int. J. Neural Syst. 13, 453–460 (2003)

J. Seul, K. Sung, Hardware implementation of a real-time neural network controller with a DSP and an FPGA for nonlinear systems. IEEE Trans. Ind. Electron. 54, 265–271 (2007)

E. Stoumpou, F.A. Khanday, C. Psychalinos, N.A. Shah, A low-voltage square-root domain nth order multifunction FLF filter topology. Analog Integr. Circuits Signal Process. 61, 315–322 (2009)

E. Stoumpou, C. Psychalinos, Square-root domain linear transformation filters. Int. J. Circuit Theory Appl. 39, 719–731 (2011)

J. von Neumann, The general and logical theory of automata, in Cerebral Mechanisms in Behavior—The Hixon Symposium, ed. by L.A. Jeffress (Wiley, New York, 1951)

R. Wagner, A. Molnar, F.S. Werblin, Analysis of the interaction between the retinal ON and OFF channels using CNN-UM models. Int. J. Circuit Theory Appl. 37, 87–108 (2009)

G.J. Yu, C.Y. Huang, B.D. Liu, J.J. Chen, Design of square-root domain filters. Analog Integr. Circuits Signal Process. 43, 49–59 (2005)

Acknowledgements

The authors would like to thank the anonymous reviewers for their constructive comments and suggestions, which enhanced the clarity of this manuscript. This research has been financed by the University Grants Commission (UGC) New Delhi India under Major Research Project Financial Assistance Scheme No. 39-558/2010 (SR), dated 10 Jan. 2011. We would like to profoundly acknowledge UGC for their support.

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Khanday, F.A., Psychalinos, C. & Shah, N.A. Square-Root-Domain Realization of Single-Cell Architecture of Complex TDCNN. Circuits Syst Signal Process 32, 959–978 (2013). https://doi.org/10.1007/s00034-012-9503-1

Received:

Revised:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s00034-012-9503-1