Abstract

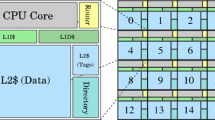

In this paper we present a cache coherence protocol formultistage interconnection network (MIN)-based multiprocessors with two distinct private caches:privateblocks caches (PCache) containing blocks private to a process andshared-blocks caches (SCache) containing data accessible by all processes. The architecture is extended by a coherence control bus connecting all shared-block cache controllers. Timing problems due to variable transit delays through the MIN are dealt with by introducingTransient states in the proposed cache coherence protocol. The impact of the coherence protocol on system performance is evaluated through a performance study of three phases. Assuming homogeneity of all nodes, a single-node queuing model (phase 3) is developed to analyze system performance. This model is solved for processor and coherence bus utilizations using the mean value analysis (MVA) technique with shared-blocks steady state probabilities (phase 1) and communication delays (phase 2) as input parameters. The performance of our system is compared to that of a system with an equivalent-sized unified cache and with a multiprocessor implementing a directory-based coherence protocol. System performance measures are verified through simulation.

Similar content being viewed by others

References

Agarwal, A., Lim, B.-H., Kranz, D., and Kubiatowicz, J. 1990. APRIL: A processor architecture for multiprocessing. InConf. Proc.—The 17th Annual Internat. Symp. on Comp. Architecture (Seattle, May 28–31), pp. 104–114.

Archibald, J.K. 1987. The cache coherency problem in shared memory multiprocessors. Ph.D. thesis and tech. rept. 87-02-06, Dept. of Comp. Sci., Univ. of Wash., Seattle.

BBN. 1989.Butterfly GP1000 Switch Tutorial. BBN Advanced Computers, Inc.

Bhuyan, L.N., Liu, B., and Ahmed, I. 1989. Analysis of MIN based-multiprocessors with private cache memories. InConf. Proc. — The 1989 Internat. Conf. on Parallel Processing (St. Charles, Ill., Aug. 14–18), Penn. State Univ. Press, vol. 1, pp. 51–58.

Censier, L.M., and Feautrier, P. 1978. A new solution to coherence problems in multicache systems.IEEE Trans. Comps., C-27, 12 (Dec.): 1112–1118.

Cheong, H., and Veidenbaum, A.V. 1988. A cache coherence scheme with fest selective invalidation. InConf. Proc.—The 15th Annual Internat. Symp. on Comp. Architecture (Honolulu, May 30–June 2), pp. 299–307.

Dubois, M., and Briggs, F.A. 1982. Effects of cache coherency in multiprocessors.IEEE Trans. Comps., C-31, 11 (Nov.): 1083–1099.

Eggers, S. 1989. Simulation analysis of data sharing in shared memory multiprocessors. Ph.D. thesis and tech. rept. UCB/CSD 89/501, Univ. of Calif., Berkeley.

Goodman, J.R., and Woest, P.J. 1988. The Wisconsin multicube: A new large-scale cache-coherent multiprocessor. InConf. Proc.—The 15th Annual Internat. Symp. on Comp. Architecture (Honolulu, May 30–June 2), pp. 422–431.

Gustavson, D.B. 1992. The scalable coherent interface and related standard projects.IEEE Micro, 12, 2 (Feb.): 10–22.

Lazowska, E., Zahorjan, J., Graham, G.S., and Sevcik, K.C. 1984.Quantitative System Performance. Prentice-Hall, New York.

Lenoski, D., Laudon,J., Gharachorloo, K., Gupta, A., and Hennessy, J. 1990. The directory-based cache coherence protocol for the DASH multiprocessor. InConf. Proc.—The 17th Annual Internat. Symp. on Comp. Architecture (Seattle, May 28–31), pp. 148–159.

Min, S.L., and Baer, J.L. 1989. A timestamp-based cache coherence scheme. InConf. Proc. — The 1989 Internat. Conf. on Parallel Processing (St. Charles Ill., Aug. 14–18), Penn. State Univ. Press, vol. 1, pp. 23–32.

Mizrahi, H.E., Baer, J.L., Lazowska, E.D., and Zahorjan, J. 1989. Extending the memory hierarchy into multiprocessor interconnection networks: A performance analysis. InConf. Proc. — The 1989 Internat. Conf. on Parallel Processing (St. Charles, Ill., Aug. 14–18), Penn. State Univ. Press, vol. 1, pp. 41–50.

Smith, A.J. 1982. Cache memories.ACM Comp. Surveys, 14, 3 (Sept.): 473–530.

Smith, A.J. 1985. CPU cache consistency with software support and using one time identifiers. InConf. Proc. of the 1985 Pacific Comp. Commun. Symp. (Seoul, S. Korea, Oct. 22–24), pp. 153–161.

Stenström, P. 1989. A cache consistency protocol for multiprocessors with multistage networks. InConf. Proc. — The 16th Annual Internat. Symp. on Comp. Architecture (Jerusalem, Israel, May 28–June 1), pp. 407–415.

Tang, C.K. 1976. Cache system design in the tightly coupled multiprocessor system. InConf. Proc. — The 1976 AFIPS Nat. Comp. Conf., pp. 749–753.

Trivedi, K.S. 1982.Probability & Statistics with Reliability, Queuing, and Computer Science Applications. Prentice-Hall, New York.

Yen, W.C., and Fu, K.S. 1982. Analysis of multiprocessor cache organizations with alternative main memory update policies. InConf. Proc. of the 9th Annual Internat. Symp. on Comp. Architecture (Austin, Tex., Apr. 26–29), pp. 89–100.

Yousif, M.S. 1991. Effective use of caches in MIN-based multiprocessors. Ph.D. thesis, Dept. of Electrical and Comp. Engineering, Penn. State Univ., University Park, Penn.

Author information

Authors and Affiliations

Rights and permissions

About this article

Cite this article

Yousif, M.S., Das, C.R. & Thazhuthaveetil, M.J. A Cache coherence protocol for MIN-based multiprocessors. J Supercomput 8, 163–185 (1994). https://doi.org/10.1007/BF01204660

Received:

Accepted:

Issue Date:

DOI: https://doi.org/10.1007/BF01204660