Abstract

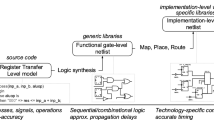

Die shrinking combined with the non-ideal scaling of voltage increases the probability of MOS transistors to encounter HCI. This mechanism causes timing degradation and possibly failures in ICs. The evaluation of timing degradation early in the design flow becomes a must-have to ensure the expected time-to-market and IC lifetime. In this paper, we propose a framework for simulating and analyzing the HCI-induced timing variations at high abstraction level. We first present a bottom-up approach to move information about timing degradation up to the higher abstraction layers. Then, we describe a simulation framework for analyzing the HCI-induced timing variations, and we evaluate its performance and accuracy. Finally, by considering a sample processor, we analyze the impact of the instruction set architecture on slack times and critical paths.

Similar content being viewed by others

References

Accellera Systems Initiative (2009) SystemC 2.2

Araujo C, Gomes M, Barros E, Rigo S, Azevedo R, Araujo G (2007) Platform designer: an approach for modeling multiprocessor platforms based on SystemC. In: Design automation for embedded systems Proc, vol 10, pp 253–283

Bechara C, Berhault A, Ventroux N, Chevobbe S, Lhuillier Y, David R, Etiemble D (2011) A small footprint interleaved multithreaded processor for embedded systems. In: IEEE ICECS Proc, pp 685–690

Bechara C, Ventroux N, Etiemble D (2010) Towards a parameterizable cycle-accurate ISS in ArchC. In: ACS/IEEE AICCSA Proc, pp 1–7

Beltrame G, Bolchini C, Fossati L, Miele A, Sciuto D (2008) ReSP: a non-intrusive transaction-level reflective MPSoC simulation platform for design space exploration. In: ASP-DAC Proc, pp 673–678

Bernstein JB, Gurfinkel M, Li X, Walters J, Shapira Y, Talmor M (2006) Electronic circuit reliability modelling. In: Elsevier microelectronics reliability Journ, vol 46, pp 1957–1979

Bertolini C, Heron O, Ventroux N, Marc F (2012) Relation between HCI-induced performance degradation and applications in a RISC processor. In: IEEE IOLTS Proc. (to appear)

Bravaix A, Guerin C, Huard V, Roy D, Roux J, Vincent E (2009) Hot-Carrier acceleration factors for low power management in DC-AC stressed 40 nm NMOS node at high temperature. In: IEEE IRPS Proc, pp 531–548

Brooks D, Dick RP, Joseph R, Shang L (2007) Power, thermal, and reliability modeling in nanometer-scale microprocessors. In: IEEE Micro, vol 27, pp 49–62

Coskun AK, Rosing TS, Leblebici Y, Micheli GD (2006) A simulation methodology for reliability analysis in multi-core SoCs. In: GLSVLSI Proc, pp 95–99

Fang J, Sapatnekar S (2011) Scalable methods for analyzing the circuit failure probability due to gate oxide breakdown. In: IEEE transactions on VLSI systems, vol 20, pp 1960–1973

Gupta T, Bertolini C, Heron O, Ventroux N, Zimmer T, Marc F (2010) RAAPS: Reliability aware ArchC based processor simulator. In: IEEE IIRW Proc, pp 153–156

Gupta T, Heron O, Ventroux N, Zimmer T, Marc F, Bertolini C (2012) Impact of power consumption and temperature on processor lifetime reliability. In: Journal of low power electronics (JOLPE), vol 8, pp 83–94

Guthaus M, Ringenberg J, Ernst D, Austin T, Mudge T, Brown R (2001) MiBench: a free, commercially representative embedded benchmark suite. In: IEEE WWC-4, pp 3–14

Hennessy J, Patterson DA (2003) Computer architecture: a quanitative approach, 3rd edn. Morgan Kaufmann

Huang L, Xu Q (2010) AgeSim: a simulation framework for evaluating the lifetime reliability of processor-based SoCs. In: ACM DATE Proc, pp 51–56

Huard V, Ruiz N, Cacho F, Pion E (2011) A bottom-up approach for system-on-chip reliability. In: Elsevier microelectronics reliability, vol 51, pp 1425–1439

International technology roadmap for semiconductors (2009) Process integration, devices, and structures (Ed.)

Joint Electron Device Engineering Council (2010) Failure mechanisms and models for semiconductor devices. JEDEC publication no JEP122F

Kavvadias N, Nikolaidis S (2008) Elimination of overhead operations in complex loop structures for embedded microprocessors. In: IEEE Trans Comput, vol 57, pp 200–214

Lee P, Kuo M, Seki K, Lo P, Hu C (1988) Circuit aging simulator (CAS). In: IEDM technical digest, pp 134–137

Lorenz D, Barke M, Schlichtmann U (2010) Aging analysis at gate and macro cell level. In: IEEE/ACM ICCAD Proc, pp 77–84

Lu Y, Shang L, Zhou H, Zhu H, Yang F, Zeng X (2009) Statistical reliability analysis under process variation and aging effects. In: ACM/IEEE DAC Proc, pp 514–519

MentorGraphics (2011) Model technology ModelSim SE 10.0d

Po LM, Ma WC (1996) A novel four-step search algorithm for fast block motion estimation. In: IEEE trans on circuits and systems for video technology, vol 6, pp 313–317

Rigo S, Araujo G, Bartholomeu M, Azevedo R (2004) ArchC: a SystemC based architecture description language. In: SBAC-PAD Proc, pp 66–73

de Schultz MR, Mendonca AKI, Carvalho FG, Furtado OJV, Santos LCV (2007) Automatically-retargetable model-driven tools for embedded code inspection in SoCs. In: MWSCAS Proc, pp 245–248

Shin J, Zyuban V, Hu Z, Rivers JA, Bose P (2007) A framework for architecture-level lifetime reliability modeling. In: IEEE/IFIP DSN Proc, pp 534–543

Srinivasan J, Adve SV, Bose P, Rivers JA (2005) Lifetime reliability: toward an architectural solution. IEEE Micro Journ 25(3):70–80

Synopsys (2008) Design Compiler B-2008.09-SP1

Synopsys (2008) PrimeTime PX 2008.12

Takeda E, Suzuki N (1983) An empirical model for device degradation due to Hot-Carrier Injection. In: IEEE electron device letters, vol 4, pp 111–113

Tu R, Rosenbaum E, Chan W, Li C, Minami E, Quader K, Ko PK, Hu C (1993) Berkeley reliability tools-BERT. In: Trans on computer-aided design of integrated circuits and systems, vol 12, pp 1524–1534

Ventroux N, Guerre A, Sassolas T, Moutaoukil L, Blanc G, Bechara C, David R (2010) SESAM: an MPSoC simulation environment for dynamic application processing. In: IEEE international conference on embedded software and systems (ICESS)

Ventroux N, Sassolas T, David R, Blanc G, Guerre A, Bechara C (2010) SESAM extension for fast MPSoC architectural exploration and dynamic streaming application. In: IEEE/IFIP international conference on VLSI and system-on-chip (VLSI-SoC)

Author information

Authors and Affiliations

Corresponding author

Additional information

Responsible Editor: D. Gizopoulos

Rights and permissions

About this article

Cite this article

Heron, O., Bertolini, C., Sandionigi, C. et al. On the Simulation of HCI-Induced Variations of IC Timings at High Level. J Electron Test 29, 127–141 (2013). https://doi.org/10.1007/s10836-013-5368-x

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10836-013-5368-x