Abstract

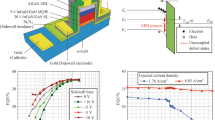

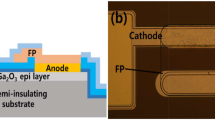

We report on the fabrication of high performance InP-based devices on an exact (001)Si-substrate. On an InP-on-Si quasi-substrate, the growth of superlattices and low-temperature InAlAs buffer for surface and device layer improvement is investigated. The selected device examples are an InGaAsP PIN diode and an (In)AlAs/In(Ga)As resonant tunnelling diodes. The functionality of these examples relies sensitively on sharp interfaces of ultra thin layers and a high optical quality of epitaxially grown III/V layers silicon substrates. A qualitative improvement is obtained for a low-temperature InAlAs buffer layer grown prior to the of device layers. Based on device models extracted from the fabricated devices a potentially low-cost optical receiver circuit on a Si-substrate is proposed and simulated using HSPICE up to 10 Gbit/s.

Similar content being viewed by others

References

M. Kai, R. Urata, D.A. B Miller, J.S. Harria, IEEE J. Quantum Electron. QE-40, 800 (2004)

Y.T. Sun, J. Napierala, S. Lourdudoss, Selective area growth of InP on InP precoated silicon substrate by hydride vapor phase epitaxy, IEEE Proc. 14th Indium Phosphide and Related Materials Conference, Sweden, 12–16 May 2002, pp. 339–342

D.J. Paul, Semicond. Sci. Technol. 19, R75 (2004) PII: S0268-1242(04)61523-9

J.D. Schaub, S.J. Koester, G. Dehlinger, Q.C. Ouyang, D. Guckenberger, Y. Min, D.L. Rogers, J. Chu, A. Grill, High-speed lateral PIN photodiodes in silicon technologies, Proc. Int. Soc. Opt. Eng., USA, Vol. 5353 (2004), pp. 1–11

S.C. Tan, Y.C. Chan, N.S.M. Lui, IEEE Trans. Adv. Packaging 29, 570 (2006)

U. Gosele, III-V materials integration technologies: wafer bonding approaches, IEEE Proc. Int. Conf. Indium Phosphide and Related Materials, Williamsburg, 14–18 May 2000, pp. 9–12

T. Nakahara, H. Tsuda, N. Ishihara, K. Tateno, C. Amano, Electron. Lett. 37, 781 (2001)

J.P. Van der Ziel, R.D. Dupuis, R.A. Logan, C. Pinzone, Appl. Phys. Lett. 51, 89 (1987)

T. Sasaki, H. Mori, M. Tachikawa, T. Yamada, J. Appl. Phys. 84, 6725 (1998)

B. Gerard, X. Marcadet, P. Etienne, D. Pribat, J. Nagle, F. Carlin, M. Ilegems, D. Friedrich, J. Eichholz, H. Bernt, MRS Symp. Proc. Ser. 533, FF4.2 (1998)

K. Linthicum, T. Gehrke, D. Thomson, E. Carlson, P. Rajoagopal, T. Smith, D. Batchelor, R. Davis, Appl. Phys. Lett. 75, 196 (1999)

M. Sugo, H. Mori, Y. Sakai, Y. Itoh, Appl. Phys. Lett. 60, 472 (1992)

R.D. Bringans, D.K. Biegelsen, L.-E. Swartz, Phys. Rev. B 44, 3054 (1991)

O. Parillaud, E. Gil-Lafon, B. Gerard, P. Etienne, D. Pribat, Phys. Lett. 68, 2654 (1996)

D. Zubia, S.D. Hersee, J. Appl. Phys. 85, 6492 (1999)

A. Bakin, D. Piester, I. Behrens, H.-H. Wehmann, E. Peiner, A. Ivanov, D. Fehly, A. Schlaschetzki, Growth of InP Layers on Nanometer-Scale Patterned Si Substrate, in: Crystal Growth and Design (2003), vol. 3, pp. 89–93

S. Neumann, A. Bakin, W. Prost, H.-H. Wehmann, A. Schlachetzki, F.-J. Tegude, J. Cryst. Growth 248, 380 (2003)

V. Khorenko, A.-C. Mofor, A. Bakin, S. Neumann, A. Guttzeit, H.H. Wehmann, W. Prost, A. Schlachetzki, F.J. Tegude, Buffer Optimization for InP-on-Si(001) Quasi-Substrates, 16th InP & Related Materials Conference, Kagoshima City, Japan, May 31 to June 4, (2004)

P. Velling, M. Agethen, W. Prost, F.J. Tegude, J. Cryst. Growth 221, 722 (2000)

K. Asai, K. Fujita, Y. Shiba, Japan. J. Appl. Phys. 60, L1967 (1991)

K. Samonji, H. Yonezu, Y. Takagi, K. Iwaki, N. Ohshima, J.K. Shin, K. Pak, Appl. Phys. Lett. 69, 100 (1996)

J.W. Mattews, A.E. Blakeslee, J. Cryst. Growth 27, 118 (1974)

D.C. Houghton, M. Davies, M. Dion, Appl. Phys. Lett. 64, 505 (1994)

G.W. Pickell, K.L. Chang, J.H. Epple, K.Y. Cheng, K.C. Hsieh, J. Vac. Sci. Technol. B 18, 2611 (2000)

S. Muto, T. Inata, Semicond. Sci. Technol. 9, 1157 (1994)

C. Pacha, U. Auer, C. Burwick, P. Glösekötter, A. Brennemann, W. Prost, F.J. Tegude, K.F. Goser, Threshold Logic Circuit Design of Parallel Adders Using Resonant Tunneling Devices, IEEE Transactions on Very Large Scale Integration Systems, Vol. 8 (2000), pp. 558–572

D. Fehly, A. Schlachetzki, A. Bakin, A. Guttzeit, H.-H. Wehmann, J. Quantum Electron. QE-37, 1246 (2001)

A. Poloczek, A. Stöhr, W. Prost, I. Regolin, D. Jäger, F.-J. Tegude, High Performance III/V PIN-Diode on a Silicon(001) Substrate for Optoelectronic Receivers, 2006 European ISIS Workshop, Boppard am Rhein, Germany, May 29 (2006)

K. Sano, K. Murata, T. Otsuji, T. Akeyoshi, N. Shimizu, E. Sano, IEEE J. Sol. State Circuits 36, 281 (2001)

Z. Yan, M.J. Deen, IEEE Trans. Computer-Aided Design Int. Circuits Systems 2, 167 (1995)

Final Report Quantum Tunneling Device Technology on Silicon, QUDOS, IST-2001-32358

Author information

Authors and Affiliations

Corresponding author

Additional information

PACS

73.40.Kp; 73.43.Jn; 73.61.Ey; 78.70.Ck; 78.70.Gq

Rights and permissions

About this article

Cite this article

Prost, W., Khorenko, V., Mofor, AC. et al. High performance III/V RTD and PIN diode on a silicon (001) substrate. Appl. Phys. A 87, 539–544 (2007). https://doi.org/10.1007/s00339-007-3920-1

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s00339-007-3920-1