Abstract

This article presents a theory for the bi-decomposition of functions in multi-valued logic (MVL). MVL functions are applied in logic design of multi-valued circuits and machine learning applications. Bi-decomposition is a method to decompose a function into two decomposition functions that are connected by a two-input operator called gate. Each of the decomposition functions depends on fewer variables than the original function. Recursive bi-decomposition represents a function as a structure of interconnected gates. For logic synthesis, the type of the gate can be chosen so that it has an efficient hardware representation. For machine learning, gates are selected to represent simple and understandable classification rules.

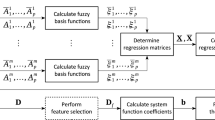

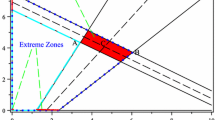

Algorithms are presented for non-disjoint bi-decomposition, where the decomposition functions may share variables with each other. Bi-decomposition is discussed for the min- and max-operators. To describe the MVL bi-decomposition theory, the notion of incompletely specified functions is generalized to function intervals. The application of MVL differential calculus leads to particular efficient algorithms. To ensure complete recursive decomposition, separation is introduced as a new concept to simplify non-decomposable functions. Multi-decomposition is presented as an example of separation.

The decomposition algorithms are implemented in a decomposition system called YADE. MVL test functions from logic synthesis and machine learning applications are decomposed. The results are compared to other decomposers. It is verified that YADE finds decompositions of superior quality by bi-decomposition of MVL function sets.

Similar content being viewed by others

References

Blake, C. & Merz, C. (1998). UCI Repository of Machine Learning Databases. University of California, Irvine, Department of Information and Computer Sciences, Irvine, USA, URL http://www.ics.uci.edu/~mlearn/MLRepository.html.

Brayton, R. & Khatri, S. (1999). Multi-valued Logic Synthesis. In 12th International Conference on VLSI Design, 196–206.

Cendrowska, J. (1987). PRISM: An Algorithm for Inducing Modular Rules. International Journal of Man-Machine Studies 27: 349–370.

Dhaou, I. B., Dubrova, E. & Tenhunen, H. (2001). Power Efficient Inter-Module Communication for Digit-Serial DSP Architectures in Deep-Submicron Technology. In 31th IEEE International Symposium on Multiple-Valued Logic, 61–66. Warsaw, Poland.

Dubrova, E., Jiang, Y. & Brayton, R. (2001). Minimization of Multiple-Valued Functions in Post Algebra. In 10th International Workshop on Logic & Synthesis, 132–137. Granlibakken, USA.

Gao, M. & Brayton, R. (2001). Multi-Valued Multi-Level Network Decomposition. In 10th International Workshop on Logic & Synthesis, 254–260. Granlibakken, USA.

Gao, M., Jiang, J., Jiang, Y., Li, Y., Sinha, S. & Brayton, R.: 2001, MVSIS. In 10th International Workshop on Logic & Synthesis, 138–143. Granlibakken, USA.

Han, S., Choi, Y. & Kim, H. (2001). A 4-Digit CMOS Quaternary to Analog Converter with Current Switch and Neuron MOS Down-Literal Circuit. In 31th IEEE International Symposium on Multiple-Valued Logic, 67–71. Warsaw, Poland.

Hanyu, T. & Kameyama, M. (1995). A 200 MHz Pipelined Multiplier Using 1.5 V-supply Multiple-valued MOS Current Mode Circuits with Dual-rail Source-coupled Logic. IEEE Journal of Solid-State Circuits 30(11): 1239–1245.

Inaba, M., Tanno, K. & Ishizuka, O. (2001). Realization of NMAX and NMIN Functions with Multi-Valued Voltage Comparators. In 31th IEEE International Symposium on Multiple-Valued Logic, 27–32. Warsaw, Poland.

Inc., R. Rambus Signaling Technologies – RSL, QRSL and SerDes Technology Overview. Rambus Inc. URL http://www.rdram.com/.

Kameyama, M. (1999). Innovation of Intelligent Integrated Systems Architecture – Future Challenge –. In Extended Abstracts of the 8th International Workshop on Post-Binary Ultra-Large-Scale Integration Systems, 1–4.

Koutsofios, E. & North, S. (1996). Drawing Graphs with Dot. AT&T Bell Labs, URL http://www.research.att.com/sw/tools/graphviz/.

Lang, C. (2003). Bi-Decomposition of Function Sets using Multi-Valued Logic. Dissertation thesis, Freiberg University of Mining and Technology, Germany.

Lang, C. & Steinbach, B. (2001). Decomposition of Multi-Valued Functions into Min-and Max-Gates. In 31th IEEE International Symposium on Multiple-Valued Logic, 173–178. Warsaw, Poland.

Mishchenko, A., Files, C., Perkowski, M., Steinbach, B. & Dorotska, C. (2000). Implicit Algorithms for Multi-Valued Input Support Minimization. In 4th International Workshop on Boolean Problems, 9–21. Freiberg, Germany.

Mishchenko, A., Steinbach, B. & Perkowski, M. (2001a). An Algorithm for Bi-Decomposition of Logic Functions. In 38th Design Automation Conference, 18–22. Las Vegas, USA.

Mishchenko, A., Steinbach, B. & Perkowski, M. (2001b). Bi-Decomposition of Multi-Valued Relations. In 10th International Workshop on Logic & Synthesis, 35–40. Granlibakken, USA.

Portland Logic and Optimization Group, ‘POLO Web Page’. Portland State University. URL http://www.ee.pdx.edu/~polo/.

Ricco, B. et al. (1998). Non-volatile Multilevel Memories for Digital Applications. Proceedings IEEE 86(12): 2399–2421.

Smith, K. (1981). The Prospects for Multivalued Logic: A Technology and Applications View. IEEE Transactions on Computers C-30(9): 619–634.

Takagi, N. & Nakashima, K. (2000). Some Properties of Discrete Interval Truth Valued Logic. In 30th IEEE International Symposium on Multiple-Valued Logic, 101–106. Portland, USA.

Teng, H. & Bolton, R. (2001). The Use of Arithmetic Operators in a Self-Restored Current-Mode CMOS Multiple-Valued Logic Design Architecture. In 31th IEEE International Symposium on Multiple-Valued Logic, 100–105. Warsaw, Poland.

Uemura, T. & Baba, T. (2001). A Three-Valued D-Flip-Flop and Shift Register Using Multiple-Junction Surface Tunnel Transistors. In 31th IEEE International Symposium on Multiple-Valued Logic, 89–93. Warsaw, Poland.

Waho, T., Hattori, K. & Takamatsu, Y. (2001). Flash Analog-to-Digital Converter Using Resonant-Tunneling Multiple-Valued Circuits. In 31th IEEE International Symposium on Multiple-Valued Logic, 94–99. Warsaw, Poland.

Yanushkevich, S. (1998). Logic Differential Calculus in Multi-Valued Logic Design. Habilitation thesis, Technical University of Szczecin, Poland.

Zupan, B. (1997). Machine Learning Based on Function Decomposition. Ph.D. thesis, University of Ljubljana, Ljubljana, Slowenia.

Author information

Authors and Affiliations

Rights and permissions

About this article

Cite this article

Lang, C., Steinbach, B. Bi-Decomposition of Function Sets in Multiple-Valued Logic for Circuit Design and Data Mining. Artificial Intelligence Review 20, 233–267 (2003). https://doi.org/10.1023/B:AIRE.0000006608.31990.cd

Issue Date:

DOI: https://doi.org/10.1023/B:AIRE.0000006608.31990.cd