Abstract

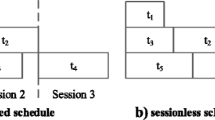

With shrinking device sizes, System-on-Chip (SoC) cores are growing in number and complexity. This has led to high volumes of test data and long test times. Therefore, reducing test cost by minimizing the overall test time is one of the main goals of SoC testing. To efficiently manage test resources and power dissipation, tests for the SoC cores are arranged into test schedules. Traditional SoC test methods assume a constant test frequency and supply voltage (V D D ) for the entire test schedule. However, test power and test time can be regulated by varying V D D and test clock frequency to optimize SoC test schedules for a given power budget. The research presented in this paper focuses on power-aware optimization of SoC test schedules to minimize test time by scaling the supply voltage and test clock rate. This scaling can be on a per session basis (in case of session-based test schedules) or dynamically (in case of sessionless test schedules). Exact and heuristic algorithms for solving the optimization problem are discussed. These algorithms are implemented and applied to several SoC benchmarks. Results show a significant reduction in SoC test time over the conventional test schedules where V D D and clock are fixed at given nominal values.

Similar content being viewed by others

References

Beigné E, Clermidy F, Miermont S, Vivet P (2008) Dynamic voltage and frequency scaling architecture for units integration within a GALS NoC. In: Proceeding Second ACM/IEEE international symp. networks-on-chip, pp 129–138

Chang J T Y, McCluskey E J (1996) Detecting delay flaws by very-low-voltage testing. In: Proceeding International test conf, pp 367–376

Chang J T Y, McCluskey E J (1996) Quantitative analysis of very-low-voltage testing. In: Proceeding 14th IEEE VLSI test symp., pp 332–337

Chou R M, Saluja K K, Agrawal V D (1994) Power constraint scheduling of tests. In: Proceeding 7th International conference VLSI design, pp 271–274

Chou R M, Saluja K K, Agrawal V D (1997) Scheduling tests for VLSI systems under power constraints. IEEE Trans VLSI Syst 5(2):175–185

Craig G L, Kime C R, Saluja K K (1988) Test scheduling and control for VLSI built-in self-test. IEEE Trans Comput 37(9):1099–1109

Devanathan V R, Ravikumar C P, Mehrotra R, Kamakoti V (2007) PMScan: a power-managed scan for simultaneous reduction of dynamic and leakage power during scan test. In: Proceeding International test conf., pp 1–10

Engelke P, Polian I, Renovell M, Seshadri B, Becker B (2004) The pros and cons of very-low-voltage testing: an analysis based on resistive bridging faults. In: Proceeding 22nd IEEE VLSI test symp., pp 171–178

Girard P, Nicolici N, Wen X (2010) Power-aware testing and test strategies for low power devices. Springer

Guzdial M (2016) Introduction to computing and programming in python, 4th edn. Prentice-Hall

Hao H, McCluskey E J (1993) Very-low-voltage testing for weak CMOS logic ICs. In: Proceeding international test conf., pp 275–284

Harmanani H M, Salamy H A (2006) A simulated annealing algorithm for system-on-chip test scheduling with power and precedence constraints. Int J Comput Intell Appl 6(4):511–530

Huang Y, Reddy S M, Cheng W T, Reuter P, Mukherjee N, Tsai C C, Samman O, Zaidan Y (2002) Optimal core wrapper width selection and SOC test scheduling based on 3-D bin packing algorithm. In: Proceeding International test conference, pp 74–82

International Technology Roadmap for Semiconductors 2008 Update Overview. http://www.itrs.net/Links/2008ITRS/Update/

ITC 2002 SOC Benchmarking Initiative. http://www.extra.research.philips.com/itc02socbenchm

Iyengar V, Chakrabarty K (2001) Precedence-based, preemptive and power constrained test scheduling for system-on-chip. In: Proceeding 19th IEEE VLSI test symp., pp 368–374

Iyengar V, Chakrabarty K, Marinissen E J (2002) On using rectangle packing for SOC wrapper/TAM co-optimization. In: Proceeding 20th IEEE VLSI test symp., pp 253–258

Iyengar V, Chakrabarty K, Marinissen E J (2002) Test wrapper and test access mechanism co-optimization for system-on-chip. J Electron Test Theory Appl 18:211–228

Kavousianos X, Chakrabarty K, Jain A, Parekhji R (2012) Time-division multiplexing for testing SoCs with DVS and multiple voltage islands. In: Proceeding European test symposium, pp 1–6

Kirkpatrick S Jr, Gelatt D, Vecchi M P (1983) Optimization by simulated annealing. Science 220 (4598):671–680

Koranne S (2003) Design of reconfigurable access wrappers for embedded core based SoC test. IEEE Trans VLSI Syst 11(5):955–960

Larsson E (2005) Introduction to advanced system-on-chip test design and optimization. Springer

Larsson E, Fujiwara H (2002) Power constrained preemptive TAM scheduling. In: Proceeding Seventh IEEE European test workshop, pp 119–126

Larsson E, Peng Z (2002) An integrated framework for the design and optimization of SOC test solutions. J Electron Test Theory Appl Spec Issue Plug-and-Play Test Autom System-On-Chip 18:385–400

Li J C M, Tseng C W, McCluskey E J (2001) Testing for resistive opens and stuck opens. In: Proceeding International test conf., pp 1049–1058

Marinissen E J (2013) Private communication

Millican S K, Saluja K K (2013) 3D-IC benchmarks. http://3dsocbench.ece.wisc.edu/ [Online: accessed 03-Jan-2014]

Millican S K, Saluja K K (2013) Private communication

Millican S K, Saluja K K (2014) Optimal test scheduling formulation under power constraints with dynamic voltage and frequency scaling. J Electron Test Theory Appl 30(5):569–580

Muresan V, Wang X, Muresan V, Vladutiu M (2000) A comparison of classical scheduling approaches in power-constrained block-test scheduling. In: Proceeding International test conference, pp 882–891

Nicolici N (2013) Private communication

Nose K, Sakurai T (2000) Optimization of V D D and V T H for low-power and high-speed applications. In: Proceeding Asia and South Pacific design automation conference, pp 469–474

Pouget J, Larsson E, Peng Z, Flottes M L, Rouzeyre B (2003) An efficient approach to SoC wrapper design, TAM configuration and test scheduling. In: Proceeding IEEE European test workshop, pp 51–56

Ravi S (2007) Power-aware test: challenges and solutions. In: Proceeding International test conf., pp 1–10

Sakurai T (2004) Alpha power-law MOS model. Solid-State Circ Soc Newslett 9(4):4–5

Sakurai T, Newton A R (1990) Alpha-power law MOSFET model and its applications to CMOS inverter delay and other formulas. IEEE J Solid-State Circ 25(2):584–594

Samii S, Larsson E, Chakrabarty K, Peng Z (2006) Cycle-accurate test power modeling and its application to SoC test scheduling. In: Proceeding International test conf., pp 1–10

Sehgal A, Chakrabarty K (2005) Test planning for the effective utilization of port-scalable testers for heterogeneous core-based SoCs. In: Proceeding IEEE International conference on CAD, pp 88–93

Sehgal A, Bahukudumbi S, Chakrabarty K (2008) Power-aware SoC test planning for effective utilization of port scalable testers. ACM Trans Des Autom Electron Syst 13(3):53–71

Sheshadri V (2014) Power-aware system-on-chip test optimization through frequency and voltage scaling. PhD thesis, Auburn University, ECE Department

Sheshadri V, Agrawal V D, Agrawal P (2012) Optimal power-constrained SoC test schedules with customizable clock rates. In: Proceeding 25th IEEE system-on-chip conference, pp 271–276

Sheshadri V, Agrawal V D, Agrawal P (2013) Optimum test schedule for SoC with specified clock frequencies and supply voltages. In: Proceeding 26th International conference on VLSI design, pp 267–272

Sheshadri V, Agrawal V D, Agrawal P (2013) Power-aware SoC Test optimization through dynamic voltage and frequency scaling. In: Proceeding 21st IFIP/IEEE International conf. very large scale integration (VLSI-SoC), pp 102–107

Sheshadri V, Agrawal V D, Agrawal P (2013) Session-less SoC test scheduling with frequency scaling. In: Proceeding 22nd IEEE North atlantic test workshop (NATW)

Truong D N, Cheng W H, Mohsenin T, Yu Z, Jacobson A T, Landge G, Meeuwsen M J, Watnik C, Tran A T, Xiao Z, Work E W, Webb J W, Mejia P V, Baas B M (2009) A 167-processor computational platform in 65 nm CMOS. IEEE J Solid-State Circ 44(4):1130–1144

Venkataramani P (2014) Reducing ATE test time by voltage and frequency scaling. PhD thesis, Auburn University, ECE Department

Venkataramani P, Agrawal V D (2013) Reducing test time of power constrained test by optimal selection of supply voltage. In: Proceeding 26th International conference on VLSI design, pp 273–278

Venkataramani P, Agrawal V D (2013) Test time reduction using aynchronous clocking. In: Proceeding International test conf., Paper 15.3

Venkataramani P, Sindia S, Agrawal V D (2013) A test time theorem and its applications. In: Proceeding 14th IEEE Latin-American test workshop

Venkataramani P, Sindia S, Agrawal V D (2013) Finding best voltage and frequency to shorten power-constrained test time. In: Proceeding 31st IEEE VLSI test symp., pp 19–24

Venkataramani P, Sindia S, Agrawal V D (2014) A test time theorem and its applications. J Electron Test Theory Appl 30(2):229–236

Zhao D, Huang R, Yoneda T, Fujiwara H (2007) Power-aware multi-frequency heterogeneous SoC test framework design with floor-ceiling packing. In: Proceeding IEEE ISCAS, pp 2942–2945

Zhao D, Upadhyaya S (2003) Power constrained test scheduling with dynamically varied TAM. In: Proceeding 21st IEEE VLSI test symp., pp 273–278

Zhao W, Cao Y (2006) New generation of predictive technology model for sub-45 nm early design exploration. IEEE Trans Electron Dev 53(11):2816–2823

Zorian Y (1993) A distributed control scheme for complex VLSI devices. In: Proceeding 11th IEEE VLSI test symp., pp 4–9

Zou W, Reddy S M, Pomeranz I, Huang Y (2003) SOC Test scheduling using simulated annealing. In: Proceeding 21st IEEE VLSI test symp., pp 325–330

Acknowledgments

Authors are grateful to the National Science Foundation for Grants CCF-1116213, IIP-0738088 and IIP-1266036. They express gratitude to Dr. Spencer Millican and Prof. Kewal Saluja, University of Wisconsin, Madison, for providing power profiles for ITC’02 benchmarks. They thank Erik Jan Marinissen, IMEC, Belgium, and Prof. Nicola Nicolici, McMaster University, Canada, for their valuable inputs on sessionless and session-based test scheduling, and Prof. Alice Smith, Auburn University, for guidance on optimization heuristics.

Author information

Authors and Affiliations

Corresponding author

Additional information

Responsible Editor: K. K. Saluja

Rights and permissions

About this article

Cite this article

Sheshadri, V., Agrawal, V.D. & Agrawal, P. Power-Aware Optimization of SoC Test Schedules Using Voltage and Frequency Scaling. J Electron Test 33, 171–187 (2017). https://doi.org/10.1007/s10836-017-5652-2

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10836-017-5652-2