Abstract

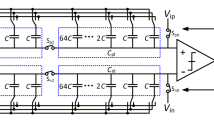

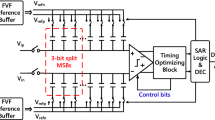

In this paper a simple method to reduce the switching energy of capacitive digital-to-analog converters (DACs) in low-power successive approximation register analog-to-digital converters (ADCs) is described. The method is based on the well-known monotonic switching procedure and the use of one intermediate voltage level during switching. Unlike most recently published switching methods the proposed method does not require the intermediate voltage to be accurate. The implementation of digital control and an intermediate voltage-level generator is considered. To evaluate the reduction in switching energy compared to the conventional monotonic switching procedure, the behavioral model of a 10-bit ADC was examined. The additional digital logic, voltage generator, and capacitive DAC were modeled at a transistor level using a 65 nm STM design kit. Simulation results and the subsequent power efficiency gains are presented.

Similar content being viewed by others

References

Murmann, B. (2016). ADC performance survey 1997–2016 [Online]. Available: http://web.stanford.edu/~murmann/adcsurvey.html.

Lange, H., Schmale, S., Knoop, B., Peters-Drolshagen, D., & Paul, S. (2015). ADC topology based on compressed sensing for low power brain monitoring. Procedia Engineering, 120, 315–319.

Atkin, E., Bulbakov, I., Ivanov, P., Ivanov, V., Malankin, E., Normanov, D., et al. (2016). Readout channel with majority logic timestamp and digital peak detector for Muon Chambers of the CBM experiment. Journal of Instrumentation, 11(12), C12069.

Liu, C. C., Chang, S. J., Huang, G. Y., & Lin, Y. Z. (2010). A 10-bit 50-ms/s sar adc with a monotonic capacitor switching procedure. IEEE Journal of Solid-State Circuits, 45(4), 731740.

Tong, X., & Ghovanloo, M. (2015). Energy-efficient switching scheme in SAR ADC for biomedical electronics. Electronics Letters, 51(9), 676678.

Liang, Y., Zhu, Z., & Ding, R. (2015). SAR ADC architecture with 98.8% reduction in switching energy over conventional scheme. Analog Integrated Circuits and Signal Processing, 84(1), 8996. https://doi.org/10.1007/s10470-015-0539-6.

Zhang, J., Ding, R., & Zhu, Z. (2016). 99.2% energy saving and high-linearity switching method for SAR ADCs. Analog Integrated Circuits and Signal Processing. https://doi.org/10.1007/s10470-016-0895-x.

Osipov, D., & Paul, S. (2016). Two advanced energy-back SAR ADC architectures with 99.21 and 99.37% reduction in switching energy. Analog Integrated Circuits and Signal Processing, 87(1), 8191. https://doi.org/10.1007/s10470-016-0707-3.

Zhu, Z., & Liang, Y. (2015). A 0.6-V 38-nW 9.4-ENOB 20-kS/s SAR ADC in 0.18- μm CMOS for medical implant devices. IEEE Transactions on Circuits and Systems I: Regular Papers, 62(9), 21672176.

Lee, P. C., Lin, J. Y., & Hsieh, C. C. (2016). A 0.4 V 1.94 fJ/conversion-step 10 bit 750 kS/s SAR ADC with input-range-adaptive switching. IEEE Transactions on Circuits and Systems I: Regular Papers, 63(12), 21492157.

Osipov, D., & Paul, S. (2016). Two-step reset method for energy-efficient SAR ADC switching schemes. Electronics Letters, 52(10), 816817.

Osipov, D., & Paul, S. (2017). Two-step monotonic switching scheme for low-power SAR ADCs. In 2017 15th IEEE International New Circuits and Systems Conference (NEWCAS), June 2017, p. 205208.

Osipov, D., & Paul, S. (2017). Low power SAR ADC with two-step switching scheme in 65 nm standard CMOS process. In 2017 IEEE 30th International Conference on Microelectronics (MIEL), Oct 2017, p. 209212.

van Elzakker, M., van Tuijl, E., Geraedts, P., Schinkel, D., Klumperink, E. A. M., & Nauta, B. (2010). A 10-bit charge-redistribution adc consuming 1.9 W at 1 ms/s. IEEE Journal of Solid-State Circuits, 45(5), 10071015.

Mostov, P. M., Neuringer, J. L., & Rigney, D. S. (1961). Optimum capacitor charging efficiency for space systems. Proceedings of the IRE, 49(5), 941948.

Paul, S., Schlaffer, A. M., & Nossek, J. A. (2000). Optimal charging of capacitors. IEEE Transactions on Circuits and Systems I: Fundamental Theory and Applications, 47(7), 10091016.

Yuan, C., & Lam, Y. (2012). Low-energy and area-efficient tri-level switching scheme for SAR ADC. Electronics Letters, 48(9), 482483.

Yuan, C., & Lam, Y. Y. H. (2013). A 281-nW 43.3 fJ/conversion-step 8-ENOB 25-kS/s asynchronous SAR ADC in 65 nm CMOS for biomedical applications. In 2013 IEEE International Symposium on Circuits and Systems (ISCAS2013), May 2013, p. 622625.

Sanyal, A., & Sun, N. (2013). SAR ADC architecture with 98% reduction in switching energy over conventional scheme. Electronics Letters, 49(4), 248250.

Tong, X., & Zhang, Y. (2015). 98.8% switching energy reduction in SAR ADC for bioelectronics application. Electronics Letters, 51(14), 10521054.

Bai, W., & Zhu, Z. (2017). A 0.5-V 9.3-ENOB 68-nW 10-kS/s SAR ADC in 0.18-μm CMOS for biomedical applications. Microelectronics Journal, 59, 4046.

Rui, M., Wenbin, B., & Zhangming, Z. (2015). An energy-efficient and highly linear switching capacitor procedure for SAR ADCs. Journal of Semiconductors, 36(5), 055014.

Liu, M. M. (2006). Demystifying switched capacitor circuits. Oxford: Newnes.

Yue, X. (2013). Determining the reliable minimum unit capacitance for the DAC capacitor array of SAR ADCs. Microelectronics Journal, 44(6), 473478.

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Osipov, D., Paul, S. Low power SAR ADC switching without the need of precise second reference. Analog Integr Circ Sig Process 97, 417–425 (2018). https://doi.org/10.1007/s10470-018-1225-2

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10470-018-1225-2