Abstract

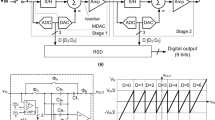

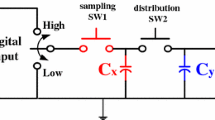

This paper presents a prototype of 14 bit 80 kSPS non-binary cyclic ADC without high accuracy analog components and complicated digital calibration. Since the redundancy of non-binary ADC tolerates the non-idealities of analog components such as capacitor mismatch and finite amplifier DC gain, the design consideration of this high accuracy ADC can be only focused on the capacitance of sampling capacitor to satisfy the overall kT/C noise target, the drivability and linearity of amplifier without any high accuracy analog components. The proposed proof-of-concept cyclic ADC has been designed and fabricated in TSMC 90 nm CMOS technology. Measured SNDR = 81.9 dB is achieved at Fs = 80 kSPS with a simple radix-value estimation technique. No other complicated digital calibration is used to compensate the non-linearity of ADC caused by MOM capacitors and a poor gain of the amplifier as low as 66 dB. Measured DNL is − 0.6/+ 0.67 LSB and INL is − 1.2/+ 1.6 LSB. Prototype ADC dissipates 8mW at supply voltage is 3.3 V in analog circuits.

Similar content being viewed by others

References

Murmann, B. (2013). Digitally assisted data converter design. In Proceedings of the ESSCIRC (ESSCIRC), Bucharest, 2013 (pp. 24–31). https://doi.org/10.1109/ESSCIRC.2013.6649063.

Suzuki, R., Maruyama, T., San, H., Aihara, K., & Hotta, M. (2013). Robust cyclic-ADC architecture based on β-expansion. IEICE Transactions on Electronics, E96–C(4), 553–559.

San, H., Sugawara, R., Hotta, M., Matsuura, T., & Aihara, K. (2017). A 12-bit 1.25 MS/s area-efficient radix-value self-estimated non-binary cyclic ADC with relaxed requirements on analog components. IEICE Transactions on Fundamentals of Electronics, Communications and Computer Sciences, E100–A(2), 534–540.

Sugawara, R., et al. (2014). Experimental implementation of non-binary cyclic ADCs with radix-value estimation algorithm. IEICE Transactions on Electronics, E97–C(4), 308–315.

Murmann, B. (2012). Thermal noise in track-and-hold circuits: Analysis and simulation techniques. IEEE Solid-State Circuits Magazine, 4(2), 46–54.

Song, B., Lee, S., & Tompsett, M. (1990). A 10-b 15-MHz CMOS recycling two-step A/D converter. IEEE Journal of Solid-State Circuits, 25(6), 1328–1338.

Vel, H., et al. (2009). A 1.2-V 250-mW 14-b 100-MS/s digitally calibrated pipeline ADC in 90-nm CMOS. IEEE Journal of Solid-State Circuits, 44(4), 1047–1056. https://doi.org/10.1109/JSSC.2009.2014702.

Miyahara, Y., et al. (2014). A 14b 60 MS/s pipelined ADC adaptively cancelling opamp gain and nonlinearity. IEEE Journal of Solid-State Circuits, 49(2), 416–425. https://doi.org/10.1109/JSSC.2013.2289902.

Acknowledgements

The authors would like to thank STARC for supporting this research.

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Watanabe, Y., Narita, H., Tsuchiya, H. et al. Experimental implementation of a 14 bit 80 kSPS non-binary cyclic ADC. Analog Integr Circ Sig Process 97, 207–214 (2018). https://doi.org/10.1007/s10470-018-1197-2

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10470-018-1197-2