Abstract

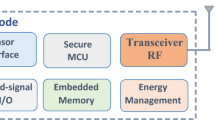

Internet of things is a topic of rising interest and intensive research, where power consumption is one of its most relevant challenges. This article presents a new radiofrequency subthreshold ultra low power LC voltage controlled oscillator (VCO). A graphical inductor optimization approach has been proposed and used to design the LC VCO leading to high performances in terms of power consumption, chip area and phase noise. It uses the adaptive body biasing technique to ensure high immunity to process, voltage and temperature variations. Realized in a 130 nm CMOS technology, the VCO occupies a total area of 0.234 mm2. The measured frequency varies between 2.34 and 2.43 GHz. The post-layout simulation results show a phase noise of −116.1 dBc/Hz @1 MHz offset frequency, while the measured phase noise is −107.36 @1 MHz due to noisy measuring environment. The presented VCO provides a measured power consumption of only 168 μW from 0.6 V supply voltage, making it suitable for ultra low power applications.

Similar content being viewed by others

Change history

25 October 2017

The original publication of the article contains an error in the author Dr. Loulou’s biography. The correct version of the biography is given below.

References

ITRS: International Technology Roadmap for Semiconductor 2.0. (2015).

Gartner. (2015). IoT rapid prototyping to proof your business case. Gartner symposium/ITxpo, Barcelona, Spain.

Pereira, P., et al. (2014). Optimal LC-VCO design through evolutionary algorithms. Analog Integrated Circuits and Signal Processing, 78(1), 99–109.

TingHsu, M., et al. (2014). Design of Sub-1mW CMOS LC VCO based on current reused topology with Q-enhancement and body-biased technique. Microelectronics Journal, 45(6), 627–633. doi:10.1016/j.mejo.2014.04.011.

Yang, C. L., & Chiang, Y. C. (2008). Low phase-noise and low-power CMOS VCO constructed in current-reused configuration. IEEE Microwave and Wireless Components Letters, 18(2), 136–138.

Hsu, M. T. (2013). Design of low phase noise and low power modified current-reused VCOs for 10 GHz applications. Microelectronics Journal, 44, 145–151.

Banchuin, R. (2014). Analysis and comprehensive analytical modeling of statistical variations in subthreshold MOSFET’s high frequency characteristics. Theoretical and Applied Electrical Engineering, 12(1), 47–57.

Fathi, D., & Nejad, A. G. (2013). Ultra-low power, low phase noise 10 GHz LC VCO in the subthreshold regime. Circuits and Systems, 4(4), 350–355.

Ueno, K. (2010). CMOS voltage and current reference circuits consisting of subthreshold MOSFETs—Micropower circuit components for power-aware LSI applications. In J. W. Swart (Ed.), Solid state circuits technologies (pp. 1–24). InTech.

Lin, H., & Chang, D. (2006). A low-voltage process corner insensitive subthreshold CMOS voltage reference circuit. IEEE international conference on integrated circuit design and technology, ICICDT 06 (pp. 1–4).

Baker, R. J. (2011). CMOS circuit design, layout, and simulation. 3rd ed., IEEE series on microelectronic systems.

Park, D., & Cho, S. (2009). Design techniques for a low-voltage VCO with wide tuning range and low sensitivity to environmental variations. IEEE Transactions on Microwave Theory and Techniques, 57(4), 767–774.

Niranjan, V. (2013).Triple well subthreshold CMOS logic using body-bias technique. IEEE international conference on signal processing, computing and control (ISPCC) (pp. 1–6).

Lee, H., & Mohammad, S. (2007). A subthreshold low phase noise CMOS LC VCO for ultra low power applications. IEEE Microwave and Wireless Components Letters, 17(11), 796–798.

Park, D. & Cho, S. (2006). An adaptive body-biased VCO with voltage boosted switched tuning in 0.5-V supply. In Proceedings of the 32nd European solid-state circuits conference ESSCIRC (pp. 444–447).

Wang, C. et al. (2011). A 0.65 mW 2.3–2.5 GHz low phase noise LC-VCO with adaptive body biasing technique. IEEE international symposium on radio-frequency integration technology RFIT (pp. 201–204).

Author information

Authors and Affiliations

Corresponding author

Additional information

A correction to this article is available online at https://doi.org/10.1007/s10470-017-1068-2.

Rights and permissions

About this article

Cite this article

Ghorbel, I., Haddad, F., Rahajandraibe, W. et al. A subthreshold low-power CMOS LC-VCO with high immunity to PVT variations. Analog Integr Circ Sig Process 93, 415–426 (2017). https://doi.org/10.1007/s10470-017-1047-7

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10470-017-1047-7