Abstract

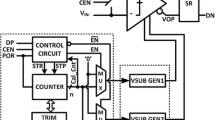

It has recently shown how a constant dc offset between two low-quality test signals can be used to test the integral nonlinearity (INL) of A/D converters (ADCs) without an accurate test stimulus, and how the same method can be used to test the INL of D/A converters (DACs) as well. We propose here an on-chip offset generator for producing the constant offset and analyse its limitations. Experimental tests on the 122 × 22 μm2 offset generator fabricated in 130 nm CMOS process show that it can be used to test the INL of 12-b DACs and ADCs. The generator is rail-to-rail capable so that almost the whole input/output range of converters can be tested. Moreover, if the proposed offset generator is used in a ratiometric test setup as proposed here as well, the influence of a reference voltage drift on measurement accuracy is cancelled out. Because of its small size, simple design, rail-to-rail capability and immunity to reference voltage changes, the proposed offset generator is well suited for built-in self-test usage.

Similar content being viewed by others

References

Bernard, S., Azais, F., Bertrand, Y., & Renovell, M. (2003). On-chip generation of ramp and triangle-wave stimuli for ADC BIST. Journal of Electronic Testing, 19(4), 469–479.

Chuang, H. M., Thei, K. B., Tsai, S. F., Lu, C. T., Liao, X. D., Lee, K. M., Chen, H. R., & Liu, W. C. (2003). A comprehensive study of polysilicon resistors for CMOS ULSI applications. Superlattices and Microstructures, 33(4), 193–208.

Dallet, D., & Machado da Silva, J. (eds) (2005). Dynamic characterisation of analogue-to-digital converters. The springer international series in engineering and computer science (Vol. 860). US: Springer.

IEEE. (2001). IEEE standard for terminology and test methods for analog-to-digital converters. IEEE Std 1241-2000.

Jin, L., Chen, D., & Geiger, R. L. (2007). SEIR linearity testing of precision A/D converters in nonstationary environments with center-symmetric interleaving. IEEE Transactions on Instrumentation and Measurement, 51(1), 138–143.

Jin, L., Parthasarathy, K., Kuyel, T., Chen, D., & Geiger, R. (2005). Accurate testing of analog-to-digital converters using low linearity signals with stimulus error identification and removal. IEEE Transactions on Instrumentation and Measurement, 54(3), 1188–1199.

Korhonen, E., Carsten, W., & Kostamovaara, J. (2010). Combining the standard histogram method and a stimulus identification algorithm for A/D converter INL testing with a low-quality sine wave stimulus. IEEE Transactions on Circuits and Systems I: Regular Papers, 57(6), 1166–1174.

Korhonen, E., Häkkinen, J., & Kostamovaara, J. (2007). A robust algorithm to identify the test stimulus in histogram-based A/D converter testing. IEEE Transactions on Instrumentation and Measurement, 56(6), 2369–2374.

Korhonen, E., & Kostamovaara, J. (2009). A loopback-based INL test method for D/A and A/D converters employing a stimulus identification technique. In Proceedings of design, automation and test in Europe conference and exhibition, Nice, France, pp. 1650–1655.

Korhonen, E., & Kostamovaara, J. (2009). On-chip offset generator for A/D converter INL testing without an accurate test stimulus. In Proceedings of the Norchip conference, Trondheim, Norway, 16–17 November 2009.

Korhonen, E., & Kostamovaara, J. (2009). Simulations and experimental results of INL testing of 16-b A/D converters without an accurate test stimulus. In Informal electronic proceedings of European test symposium. Seville, Spain.

Lee, W. T., Liao, Y. Z., Hsu, J. C., Hwang, Y. S., & Chen, J. J. (2008). A high precision ramp generator for low cost ADC test. In Proceedings of 9th International conference on solid-state and integrated-circuit technology, pp. 2103–2106.

Parthasarathy, K. L., & Geiger, R. (2001). Accurate self characterization and correction of A/D converter performance. In Proceedings of the 44th IEEE 2001 Midwest symposium on circuits and systems, Dayton, OH, Vol. 1, pp. 276–279).

Pflanzl, W. C., & Seebacher, E. (2008). Poly resistor modeling over a wide range of geometries and their different temperature and voltage behaviour for a HV CMOS process. In Proceedings of the 15th international conference on mixed design of integrated circuits and systems, Poznan, Poland, 19–21 June 2008, pp. 421–424.

Plassche, R. J. V. D. (2003). CMOS integrated analog-to-digital and digital-to-analog converters (2nd ed.). Dordrecht: Kluwer Academic Publication.

Provost, B., & Sanchez-Sinencio, E. (2003). On-chip ramp generators for mixed-signal BIST and ADC self-test. IEEE Journal of Solid-State Circuits, 38(2), 263–273.

R2_cmc standard resistor model. (2005). http://www.eigroup.org/CMC/downloads/r2_cmc/index.html.

Vasan, B. K., Duan, J., Zhao, C., Geiger, R., & Chen, D. (2009). Signal generators for cost effective BIST of ADCs. In Proceedings of the european conference on circuit theory and design, Antalya, Turkey, 23–27 August 2009, pp. 113–116.

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Korhonen, E., Kostamovaara, J. On-chip offset generator for accurate integral non-linearity testing of A/D converters and D/A-A/D converter pairs. Analog Integr Circ Sig Process 67, 21–29 (2011). https://doi.org/10.1007/s10470-010-9496-2

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10470-010-9496-2